You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The earthquake and subsequent tsunami that devastated Japan on March 11[SUP]th[/SUP], 2011 will have far reaching ramifications around the world for years to come. People have asked me how this disaster will affect the semiconductor industry so I will try and summarize it in this blog.

First the foundries:

According to TSMC: … Read More

According with the survey from GSA-Wharton design IP blocks reuse in a new IC product is 44% in average. Looking at the latest Wireless platform from TI, OMAP5, we have listed the blocks which have been (or will be) reused, coming from internal (or external) IP sourcing. For a license cost evaluation of -at least- $10M!

For those who… Read More

Apache Design Solutions today filed their S-1 with the SEC in preparation for its initial public offering (IPO). This is a big deal since there hasn’t been an IPO of an EDA company for may years (Magma was the last 10 years ago). As a private company they have not had to reveal their financials until now.

It turns out that they did… Read More

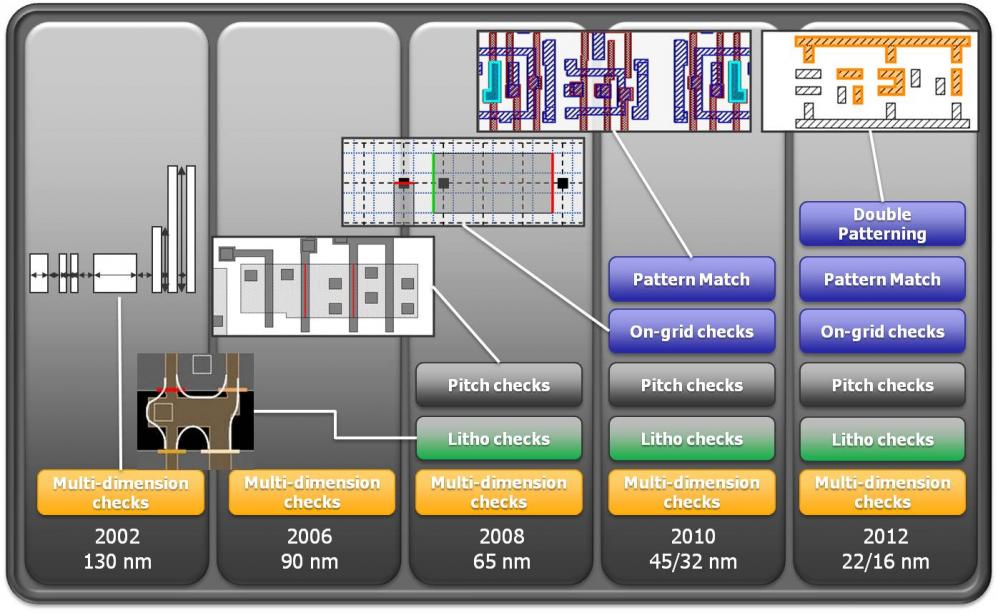

With each process generation, the design rules get more and more complex. One datapoint: there are twice as many checks at 28nm as there are at 90nm. In fact, the complexity of the rules is outpacing the ability to describe them using the simplified approaches used in the DRCs built-into layout editors or formats like LEF.

Worse still,… Read More

The semiconductor design and manufacturing challenges at 40nm and 28nm are a direct result ofMoore’s Law, the climbing transistor count and shrinking geometries. It’s a process AND design issue and the interaction is at the transistor level. Transistors may be shrinking, but atoms aren’t. So now it actually matters when even… Read More

Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout

…

Read More

…but what is the weight of the Verification IP market?

If the IP market is a niche market (see: **) with revenue of about 1% of the overall semiconductor business, how could we qualify the VIP market? Ultra-niche market? But the verification of the IP integrated into the SoC is an essential piece of the engineering puzzle when you are… Read More

There has been a lot of press this past week surrounding the release of iPad2. While it has some significant improvements, they are, for the most part, incremental. In my view the lack of flash, a USB port and a memory card slot continue to be huge deficits. Until this past week my reservations about the iPad have been mostly theoretical,… Read More

The 17[SUP]th[/SUP] Annual TSMC Technology Symposium will be held in San Jose California on April 5[SUP]th[/SUP], 2011. Dr. Morris Chang will again be the keynote speaker. The theme this year is “Trusted Technology and Capacity Provider”and I think it’s important to not only hear what people are saying but also understand why… Read More

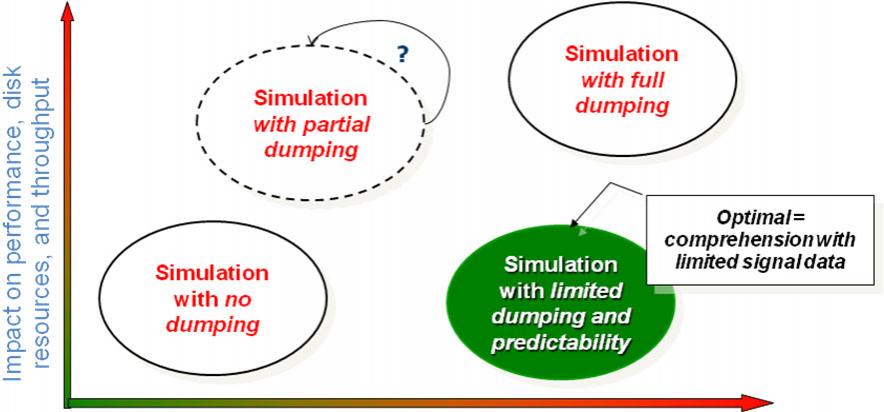

One of the challenges with verifying today’s large chips is deciding which signals to record during simulation so that you can work out the root cause when you detect something anomalous in the results. If you record too few signals, then you risk having to re-run the entire simulation when you omitted to record a signal that… Read More

AI Semiconductor Market