You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

TSMC rolled out the new reference flows for 28nm design as part of the Open Innovation Platform. The biggest surprise (to me) is that Cadence is STILL in the TSMC reference flows!

The updated TSMC OIP wiki is here, the Reference Flow 12.0 wiki can be found here, the AMS 2.0 reference flow wiki is here, and the official TSMC PR is here. … Read More

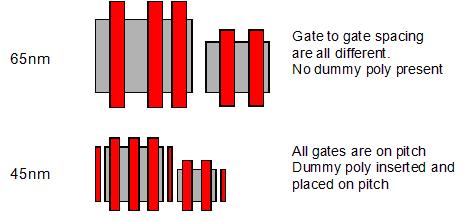

The problem:To move a single lane variable data rate SerDes (serializer-deserializer) from a 65nm process to a 45nm process, achieving a maximum performance of up to 10.3 Gbps. This is a large piece of complex mixed-signal IP with handcrafted analog circuits. Circuit performance and robustness are critical and must be maintained… Read More

3D IC @ #48DACby Daniel Nenni on 05-23-2011 at 4:54 pmCategories: EDA, Events

A three-dimensional integrated circuit (3D IC ) is a chip in which two or more layers of active electronic components are integrated both vertically and horizontally into a single circuit. The semiconductor industry is hotly pursuing this emerging technology in many different forms, as a result the full definition is still somewhat… Read More

The 48[SUP]th[/SUP] Design Automation Conference (DAC) is now upon us. DAC is billed as “the premier event for the design of electronic circuits and systems, and for EDA and silicon solutions” for which I would have to agree with 100%.

The first DAC I attended was in 1984, Albuquerque New Mexico, which was one of the first to allow … Read More

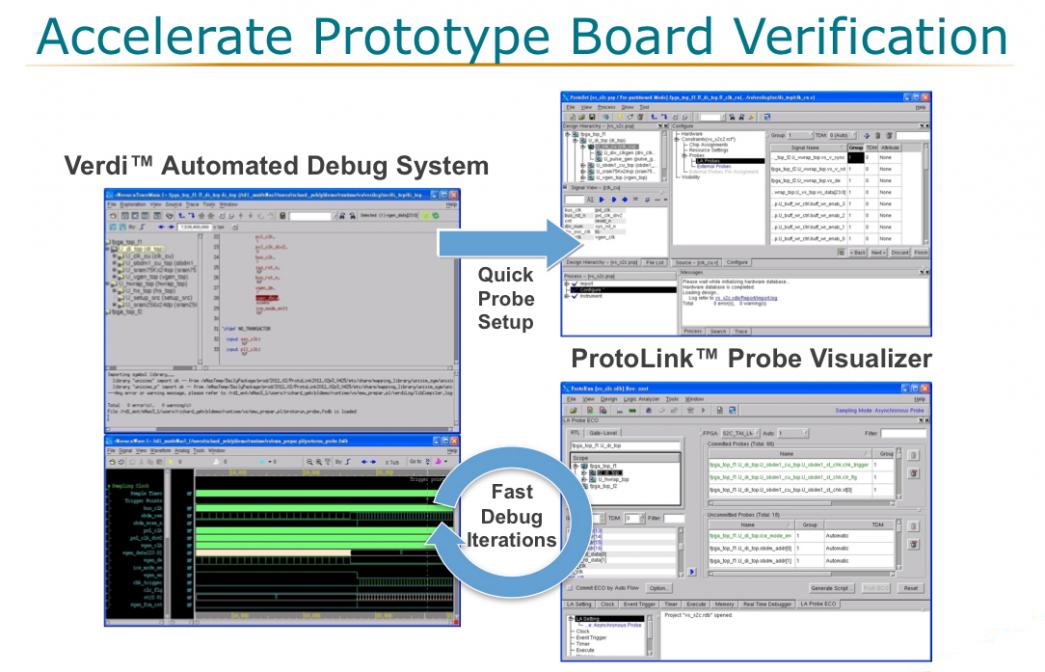

FPGA-based prototype boards are a fast, cost-effective platform for SoC system validation but they are notoriously difficult to set up and to debug. There is a big upside, however, allowing early software integration and testing and thus finding bugs in both the software and the SoC earlier. This approach is much cheaper than … Read More

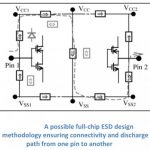

ESD has historically been a big problem analyzed with ad-hoc approaches. As explained earlier, this is no longer an adequate way to plan nor signoff ESD protection.

Pathfinder is the first full-chip comprehensive ESD planning and verification solution. It is targeted to address limitations in today’s methodologies.… Read More

Concept2Silicon Systems (C2SiS) is focused on providing complete solutions for complex SoC and System designs with best in class engineering capabilities and most cost-efficient business model. Our highly capable engineering team has experience in delivering 200+ silicon and system design solutions to its customers in … Read More

Introduction

Cadence and ClioSoft made a webinar recently and I’ll summarize what I learned from it.

What’s New from Cadence in Virtuoso 6.1.5

- Back2Basics (28nm rule integration, Skill improved with object-oriented, OASIS support, HTML Publisher, Waveform re-written for better Analog support, smaller Waveform

…

Read More

Introduction

3D field solvers produce the most accurate netlists of RC values of your IC layout that can then be used in SPICE circuit simulators however most of these solvers produce a flat netlist which tends to simulate rather slowly. Thankfully several years ago the first hierarchical SPICE tools were offered by Nassda (HSIM… Read More

Electro-static discharge (ESD) has been a problem since the beginning of IC production. Chips function on power supplies of up to a few volts (depending on the era) whereas ESD voltages are measured in the thousands of volts. When you reach out for your car door handle and a spark jumps across, that is ESD. If you were touching a chip… Read More

Build a 100% Python-based Design environment for Large SoC Designs