You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

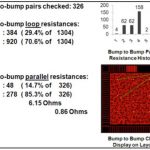

ESD has historically been a big problem analyzed with ad-hoc approaches. As explained earlier, this is no longer an adequate way to plan nor signoff ESD protection.

Pathfinder is the first full-chip comprehensive ESD planning and verification solution. It is targeted to address limitations in today’s methodologies.… Read More

Concept2Silicon Systems (C2SiS) is focused on providing complete solutions for complex SoC and System designs with best in class engineering capabilities and most cost-efficient business model. Our highly capable engineering team has experience in delivering 200+ silicon and system design solutions to its customers in … Read More

Introduction

Cadence and ClioSoft made a webinar recently and I’ll summarize what I learned from it.

What’s New from Cadence in Virtuoso 6.1.5

- Back2Basics (28nm rule integration, Skill improved with object-oriented, OASIS support, HTML Publisher, Waveform re-written for better Analog support, smaller Waveform

…

Read More

Introduction

3D field solvers produce the most accurate netlists of RC values of your IC layout that can then be used in SPICE circuit simulators however most of these solvers produce a flat netlist which tends to simulate rather slowly. Thankfully several years ago the first hierarchical SPICE tools were offered by Nassda (HSIM… Read More

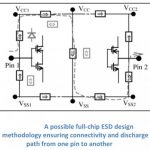

Electro-static discharge (ESD) has been a problem since the beginning of IC production. Chips function on power supplies of up to a few volts (depending on the era) whereas ESD voltages are measured in the thousands of volts. When you reach out for your car door handle and a spark jumps across, that is ESD. If you were touching a chip… Read More

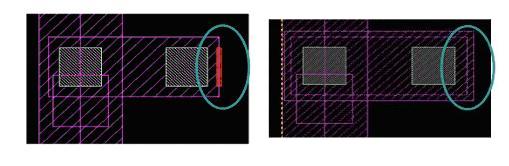

A High-Definition Multimedia Interface (HDMI) IP core was being implemented in an advanced process technology. This fairly large and complex analog mixed-signal (AMS) IP comprising over 130K devices was close to being finalized and shipped to the customer. But many design rules at the foundry were unexpectedly changed from… Read More

Reading the title you guessed it right, Mentor Graphics has three new board members today from the slate offered by billionaire activist Carl Icahn:

- José Maria Alapont, chief executive of the auto parts maker Federal-Mogul

- Gary Meyers, a director of the chip maker Exar

- David Schechter, an executive at Mr. Icahn’s investment firm

…

Read More

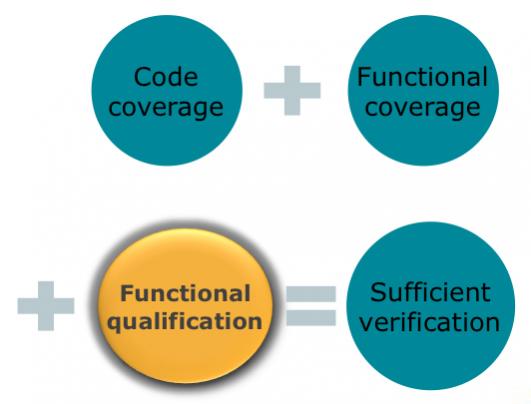

The traditional way for analyzing the effectiveness of testing in the software world and in the RTL world is code coverage. Make sure that every line of code is executed. This is a pretty crude measure since even 100% code coverage doesn’t mean that all the condition has really been tested but it is certainly necessary–after… Read More

If you just casually peruse most marketing presentations by EDA companies, you’d come to the conclusion most SoCs are designed from scratch, wrestlilng the monster to the ground with bare hands. But the reality is that most SoCs consist of perhaps 90% IP blocks (many of them memories). That still leaves the remaining 10% … Read More

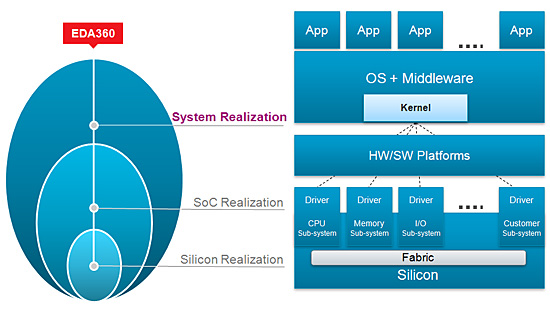

Hard to believe a year has gone by since the big announcement of the Cadence Blueprint toBattle ‘Profitability Gap’; Counters Semiconductor Industry’s Greatest Threat! Having spent more time on it that I should have, here is my opinion on EDA360 on its first anniversary.

Richard Georing did a very nice anniversary piece “Ten Key… Read More

AI Semiconductor Market