Almost no design these days is created from scratch. Typical designs can contain 500 or more IP blocks. But there is still a big difference between the first design for a new system or platform, and later designs which can be extensively based on the old design. These are known as derivatives and should be much easier to design since… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

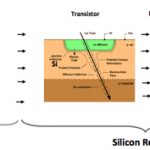

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreWe Live on a Radioactive Planet

Often as we move down the process node treadmill, new challenges appear that we didn’t really have to worry about before. Often, these challenges require addressing at a number of different levels: the process, the cell libraries, the design, the EDA tools that we use.

One well known example is the problem of metal migration.… Read More

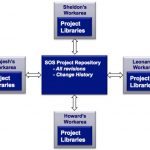

Modern Data Management

Most mixed-signal design teams don’t use data management. Well, that’s not entirely true, everyone has to do data management of some sort, it is just that it is often very ad hoc, often done by some vaguely systematic way of doing file naming, using email to keep track of changes, no access control and so on. This leads… Read More

OTP based Analog Trimming and Calibration

Embedded NVM technology based functions can be implemented in large SoC designed in advanced technology nodes down to 28nm, as there is no requirement for extra mask levels, like when integrating Nand Flash, negatively impacting the final cost. And it is also possible to integrate One Time Programmable (OTP) to store trim and … Read More

When the lines on the roadmap get closer together

Tech aficionados love roadmaps. The confidence a roadmap instills – whether using tangible evidence or just a good story – can be priceless. Decisions on “the next big thing”, sometimes years and a lot of uncertain advancements away, hinge on the ability of a technology marketing team to define and communicate a roadmap.

Any roadmap… Read More

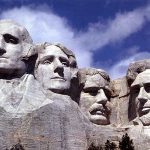

TSMC (Lincoln) vs Samsung (Clinton) vs Intel (Washington)

Usually I sleep on long flights, if not, I watch movies and read. The Lincoln movie was playing on EVA Air this week which reminded me that Abraham Lincoln was one of the greatest U.S. Presidents. If I was asked to pick a U.S. President as a spokesperson for TSMC it would be Honest Abe Lincoln. Chairman Morris Chang said it best during … Read More

Wally Rhines: Name That Graph!

Wally Rhines gave the keynote at DVCon yesterday. He started out with a game of “name that graph” which was unfortunately a bit spoiled since when the names were revealed the first line was off the top of the screen. But he extrapolated several trends such as the decreasing number of fabs (the current trend is that there… Read More

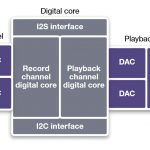

Shrinking audio creates issues and opportunities

There is a lot more to sound than meets the ear, and there a vast number of ways to deliver an audio experience. I recently trashed my gaming headset, replacing it with a Samson C03U mic and Audio-Technica ATH-PRO700MK2 headphones. It’s a huge upgrade, especially for podcasting, and I admit I was also motivated by research into digital… Read More

High and Low: High Level Synthesis and Low Power

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

Intel and Altera Sign on for 14nm

The announcement today that Intel will be a Foundry for Altera at 14nm is a significant turning point for the Semiconductor Industry and Intel’s Foundry fortunes of which the full ramifications are not likely to be understood by analysts. As a long time follower of Intel and a former co-founder of an FPGA startup (Cswitch), it has… Read More

ASML High-NA EUV is Not Ready for High-Volume Production