For a long time Cisco had a very high end product whose official internal name during its years of development was HFR, which stood for Huge F***ing Router (the marketing department insisted it stood for ‘fast’). Eventually it got given a product number, CRS-1, but not before I’d read an article about it in the Economist under its old name. Wikipedia is on it. I was at the Globalpress briefing in Santa Cruz today and Broadcom announced their next generation network processor, definitely a chip deserving of the HFC appellation.

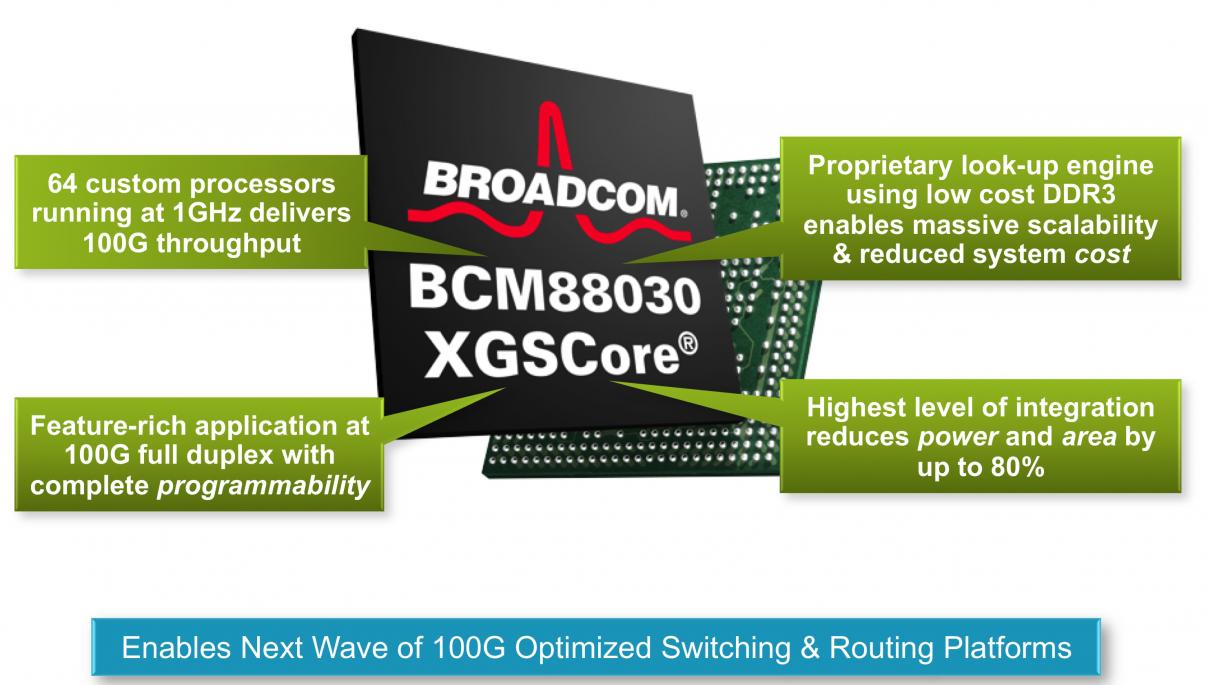

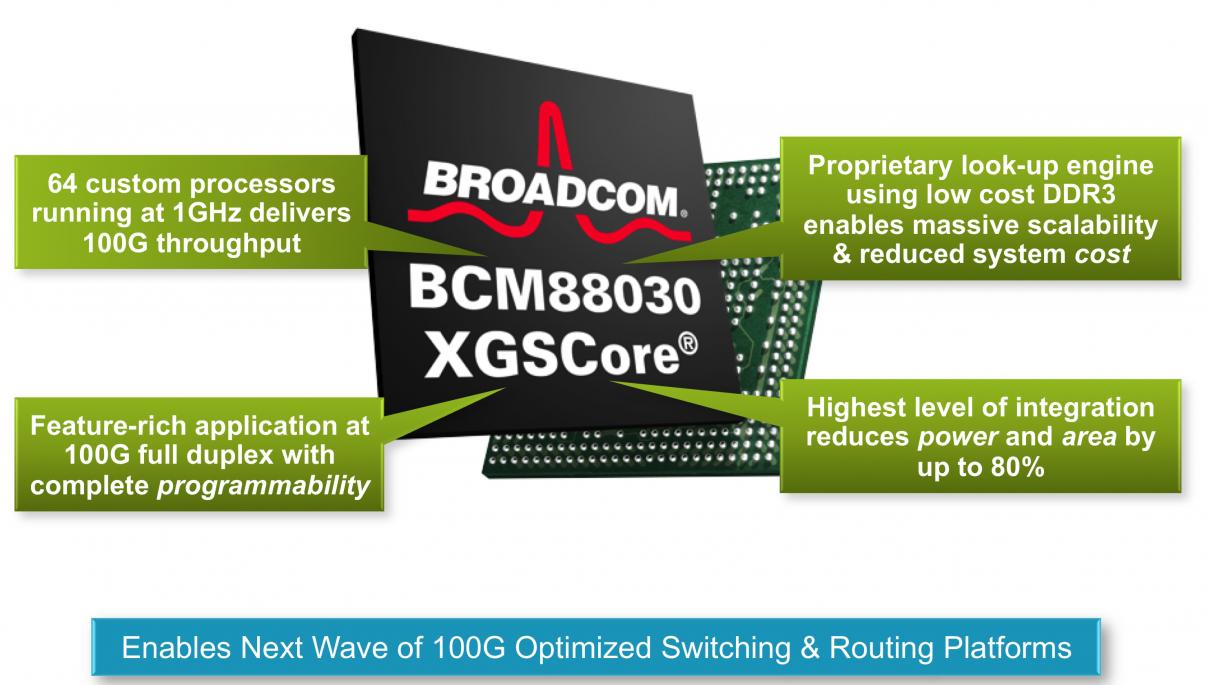

Unless you are a carrier equipment manufacturer such as Alcatel-Lucent, Ericsson or Huawei then the precise details of the chip aren’t all that absorbing. If you are, it’s called the BCM88030.

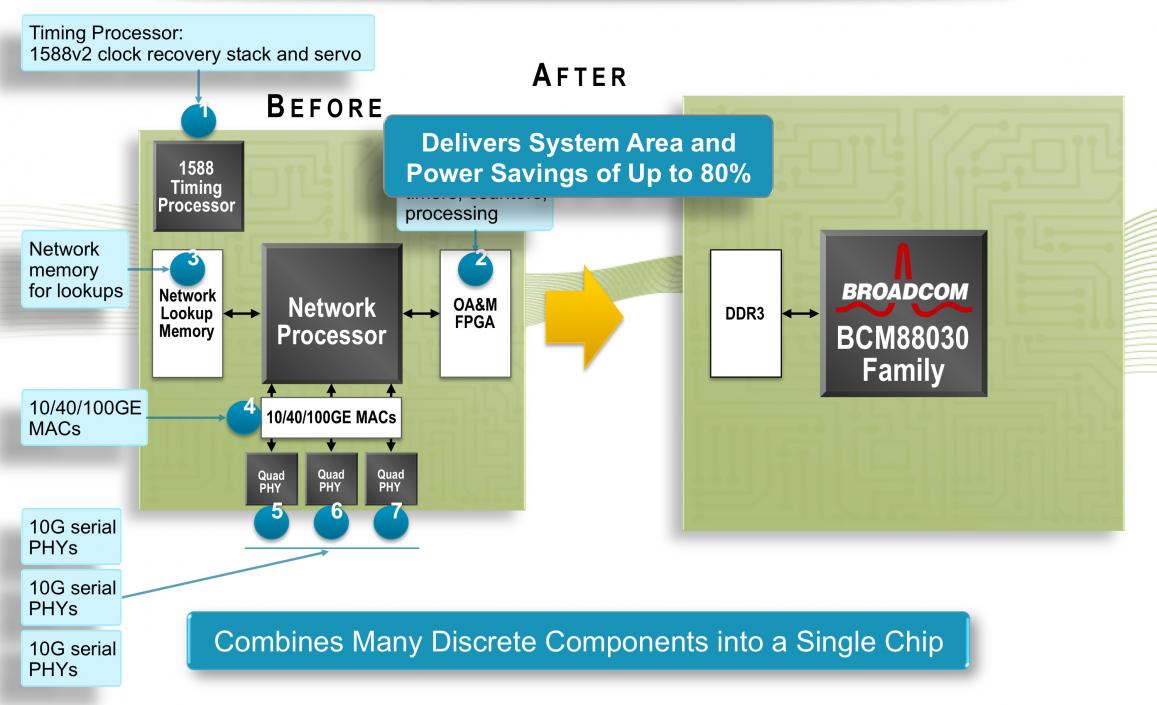

What I think is most interesting is the scale of the chip. It’s an amazing example of just what can be crammed onto a 28nm chip. Not just in size, but also in performance and power (or lack of it).

Firstly, this chip is a 100Gbps full-duplex network processor. This means it handles 300M packets/second, or a packet in approximately 3ns. Since its clock rate is 1GHz, that means in the time to execute 3 instructions so the only way this is workable is through parallelism. Indeed the chip contains 64 custom processors. Even that is not enough, each processor can handle up to 32 packets at a time, by advanced hardware multi-threading. Even that is not enough, some specialized functions just aren’t suited to general microprocessors and are offloaded to one of 7 specialized engines that perform functions like lookup (MAC addresses, IP addresses etc), police funtions, timing. All this while reducing power and area compared to previous generation solutions by 80%.

Firstly, this chip is a 100Gbps full-duplex network processor. This means it handles 300M packets/second, or a packet in approximately 3ns. Since its clock rate is 1GHz, that means in the time to execute 3 instructions so the only way this is workable is through parallelism. Indeed the chip contains 64 custom processors. Even that is not enough, each processor can handle up to 32 packets at a time, by advanced hardware multi-threading. Even that is not enough, some specialized functions just aren’t suited to general microprocessors and are offloaded to one of 7 specialized engines that perform functions like lookup (MAC addresses, IP addresses etc), police funtions, timing. All this while reducing power and area compared to previous generation solutions by 80%.

That’s just the digital dimension. The chip also contains the interfaces to the outside world with 24 10Gb/s Ethernet MACs, 6 50Gb/s Ethernet MACs and 2 100Gb/s Ethernet MACs.

What is driving the need for this amount of bandwidth is that carriers are switching completely to using Ethernet as their internal backbone between the different parts of their networks, from the base-station to the access network, to the aggregation network and in the core. This extremely high performance chip is targeted at aggregation and the core.

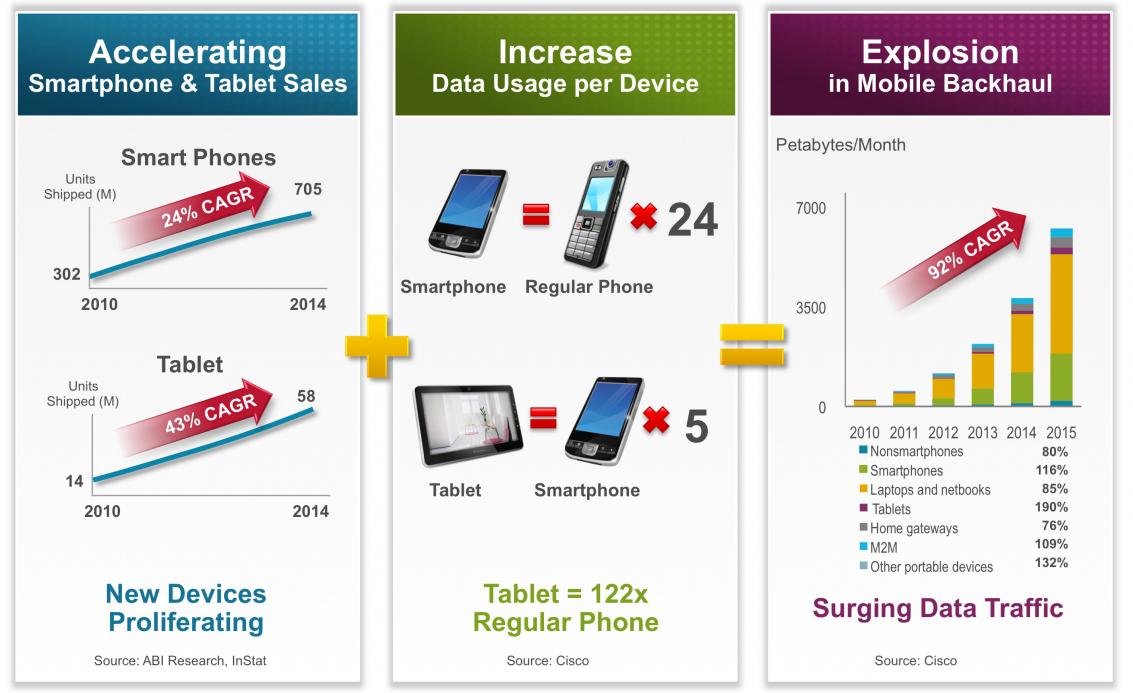

In turn this is driven by 3 main things:

- millions of smartphones and tablet computers

- upgrade of networks from 3G to 4G with increased bandwidth

- increasing use of video

These are causing an explosion in mobile backhaul, the (mostly) wired network that hooks up all the base-stations into the carriers network and to the core backbone of the internet.

The growth is quite significant. A smartphone generates 24X the data of a regular phone (I’m not sure if the includes the voice part, although in terms of bits per second that is quite low with a modern vocoder). Tablets generate 5X the data of a smartphone (and so 120X a regular phone). And the number of units is going up fast. By 2015 it is predicted that the number of connected devices will be 2X the world population. As for that video, by 2015 one million minutes of video will cross the network each second. That’s a lot of cute kittens. In total, mobile data traffic is set to increase 18 fold between 2011 and 2015.

The growth is quite significant. A smartphone generates 24X the data of a regular phone (I’m not sure if the includes the voice part, although in terms of bits per second that is quite low with a modern vocoder). Tablets generate 5X the data of a smartphone (and so 120X a regular phone). And the number of units is going up fast. By 2015 it is predicted that the number of connected devices will be 2X the world population. As for that video, by 2015 one million minutes of video will cross the network each second. That’s a lot of cute kittens. In total, mobile data traffic is set to increase 18 fold between 2011 and 2015.

This is driving 100G Ethernet adoption, forecast to have 170% CAGR over the next 5 years. Hence Broadcom’s development of this chip. But, like any other system of this complexity, the chip development is accompanied by an equally challenging software development problem, to develop a tool chain and a complete reference implementation so that customers can actually use the chip.

This is driving 100G Ethernet adoption, forecast to have 170% CAGR over the next 5 years. Hence Broadcom’s development of this chip. But, like any other system of this complexity, the chip development is accompanied by an equally challenging software development problem, to develop a tool chain and a complete reference implementation so that customers can actually use the chip.

Comments

There are no comments yet.

You must register or log in to view/post comments.