According to trusted sources it costs upwards of $50M to design a 40nm SoC down to the GDS. Semiconductor IP is a fast growing part of that equation and functional verification of that IP is critical. Hardware complexity growth continues to follow Moore’s Law but verification complexity is even more challenging. In fact, IP verification… Read More

LRCX- Coulda been worse but wasn't so relief rally- Flattish is better than downLam put in good quarter with flattish guide-…Read More

LRCX- Coulda been worse but wasn't so relief rally- Flattish is better than downLam put in good quarter with flattish guide-…Read More From Space-Central to Space-Time Balanced - A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for EmergenceA friend of SemiWiki published an article on…Read More

From Space-Central to Space-Time Balanced - A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for EmergenceA friend of SemiWiki published an article on…Read More The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

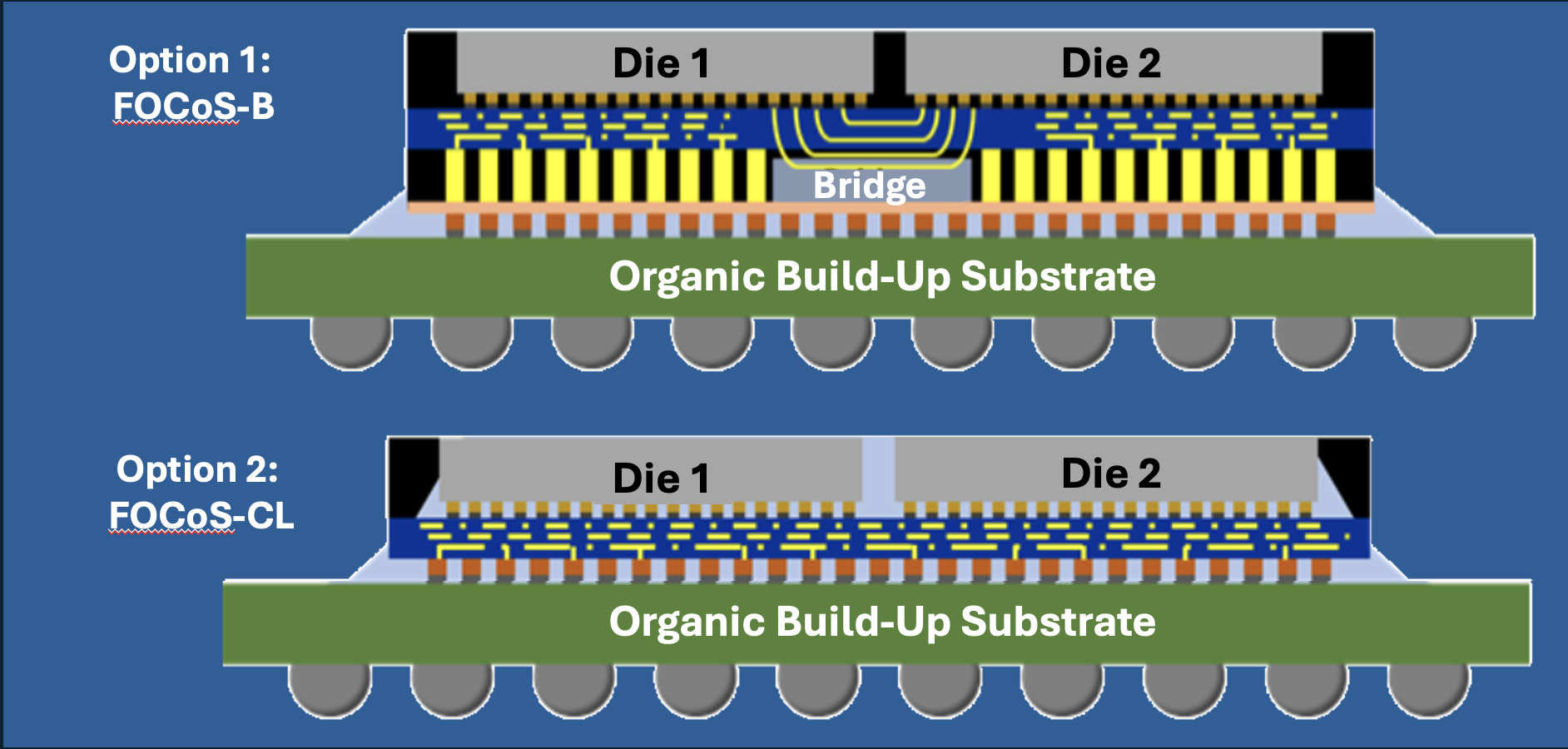

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read MoreWikiLeaks: Methodics vs IC Manage

Human nature never ceases to amaze me. I understand the recent economic turmoil and looming National Debt has thrown us for a loop but please, let us all get some perspective here and in the words of Rodney King, “Can we all get along?”

A clever little scumbag recently registered the domain danielnenni.com and is now hawking event … Read More

Apple Will Nudge Prices Down in 2012: PC Market Will Collapse

Jack Welch, the former CEO of GE, had an edict that each business unit needed to be #1 or #2 in the market or else he sold it off. HP is #1 in PC market share but it is exiting a business that it no longer can control and soon will bleed a lot of cash. HP’s Operating margin is under 6% and falling while Apple’s is at 40% and growing. So the question… Read More

HP, Palm, tablets, PCs, smartphones

Hewlett-Packard purchased Palm last year for over a billion dollars primarily to get their hands on the WebOS operating system for powering its tablets and smartphones. It’s turned out to be much too little too late. Despite WebOS being a new operating system with many attractive features, HP’s tablet offering, … Read More

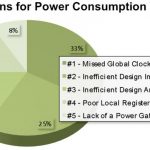

Top 5 Reasons for Wasting Power

Traditionally, David Letterman style, we should really have the top 10 reasons for wasting power in semiconductor design, but here are the five big ones.

Starting with reason #5: Lack of a power gating strategy

Leakage power is a huge proportion of total power and the only way to save leakage power (apart from low leakage cells when… Read More

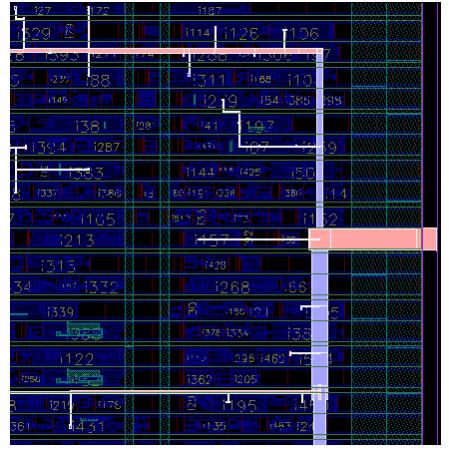

Design Constraints

Design constraints, which express higher level design intent, are one of the pieces of ancillary data that are critical to the success or failure of a custom (in fact any) design. Design constraints aren’t usually contained within layout files or library information, but without these critical data, designs may not meet specifications.… Read More

Intel’s Back to the Future Buy of Micron

In an interview that Gordon Moore gave in early 2000, the former co-founder of Intel recounted how they abandoned the DRAM market in the early 1980s in order to exit the increasingly unprofitable business and focus on the promising, yet still young x86 processor market. Intel was also home to EEPROM and NOR Flash, two memory technologies… Read More

Aug 25th in Fremont, CA – Hands on Calibre workshop: DRC, LVS, xRC, ERC, DFM

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

MUSIC in Bangalore

When you think of Indian music you might think of ragas for the sitar. But when you think of Indian MUSIC, that is the Magma user group meeting (Magma Users Summit for Integrated Circuits) coming up on September 7th in Bangalore (note: the date has changed from when it was originally announced). It is at Vivanta by Taj on M G Road.

There… Read More

Fast Track your SoC Design

Atrenta has four seminars coming up on SoC realization. More and more design is actually about finding IP and integrating it together at the block level, and then handing it off to a standard RTL to GDSII flow. The three focus areas are:

- finding quality IP faster

- accelerating IP integration and SoC assembly

- handing off RTL successfully.

AI Semiconductor Market