Clock gating is one of the most basic weapons in the armoury for reducing dynamic power on a design. All modern synthesis tools can insert clock gating cells to shut down clocking to registers when the contents of the register are not changing. The archetypal case is a register which sometimes loads a new value (when an enable signal… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreIntegrating Formal Verification into Synthesis

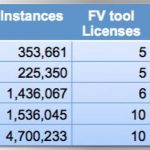

Formal verification can be used for many things, but one is to ensure that synthesis performs correctly and that the behavior of the output netlist is the same as the behavior of the input RTL. But designs are getting very large and formal verification is a complex tool to use, especially if the design is too large for the formal tool… Read More

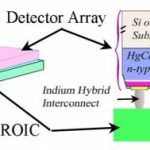

Image Sensor Design for IR at Senseeker

Image sensors are all around us with the cell phone being a popular example, and 35mm DSLR camera being another one. Last week I spoke with Kenton Veeder, an engineer at Senseeker that started his own image sensor IP and consulting services company. Instead of focusing on the consumer market, Kenton’s company does sensor … Read More

Cavium Adopts JasperGold Architectural Modeling

Cavium designs some very complex SoCs containing multiple ARM or MIPS cores at 32 and 64 bit. This complexity leads to major challenges in validating the overall chip architecture to ensure that their designs will meet the requirements of their customers once they are completed, with performance as high as 100Gbps.

Cavium have… Read More

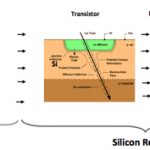

Synopsys ♥ FinFETs

FinFETs are fun! They certainly have kept me busy writing over the past year about the possibilities and probabilities of a disruptive technology that will dramatically change the semiconductor ecosystem. Now that 14nm silicon is making the rounds I will be able to start writing about the realities of FinFETs which is very exciting!… Read More

DVCon 2013 – Hope For EDA Trade Shows

Those of us who spend a lot of time at EDA marketing events cannot help but notice the dramatic shrinking of the floor space, and to some extent attendance, at the major EDA shows such as DAC and DATE. DAC used to occupy both the north and south halls of Moscone Center when in San Francisco, but now only takes up one hall. So, I did not have… Read More

TSMC ♥ Atrenta (Soft IP Webinar)

Back in 2011, TSMC announced it was extending its IP Alliance Program to include soft, or synthesizable IP. Around that time it was also announced that Atrenta’s SpyGlass platform would be used as the sole analysis tool to verify the completeness and quality of soft IP before being admitted to the program. Since then, the … Read More

SoC Derivatives Made Easier

Almost no design these days is created from scratch. Typical designs can contain 500 or more IP blocks. But there is still a big difference between the first design for a new system or platform, and later designs which can be extensively based on the old design. These are known as derivatives and should be much easier to design since… Read More

We Live on a Radioactive Planet

Often as we move down the process node treadmill, new challenges appear that we didn’t really have to worry about before. Often, these challenges require addressing at a number of different levels: the process, the cell libraries, the design, the EDA tools that we use.

One well known example is the problem of metal migration.… Read More

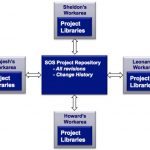

Modern Data Management

Most mixed-signal design teams don’t use data management. Well, that’s not entirely true, everyone has to do data management of some sort, it is just that it is often very ad hoc, often done by some vaguely systematic way of doing file naming, using email to keep track of changes, no access control and so on. This leads… Read More

Solving the EDA tool fragmentation crisis