Almost no design these days is created from scratch. Typical designs can contain 500 or more IP blocks. But there is still a big difference between the first design for a new system or platform, and later designs which can be extensively based on the old design. These are known as derivatives and should be much easier to design since they can leverage not just the pre-existing IP but much of the way that it has been interconnected (not to mention much or all of the software that today forms so much of the investment in an SoC).

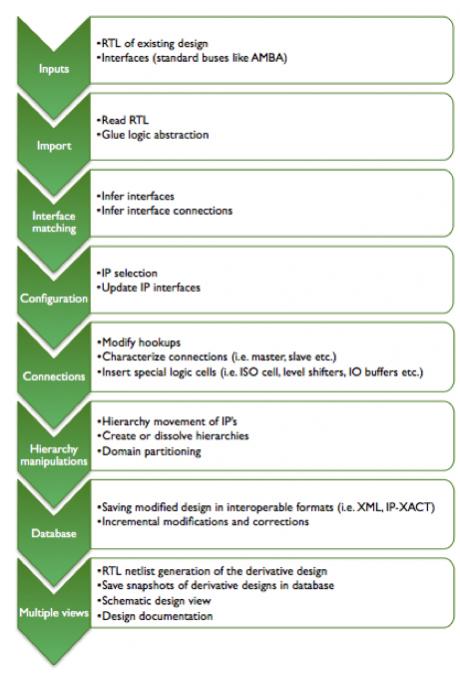

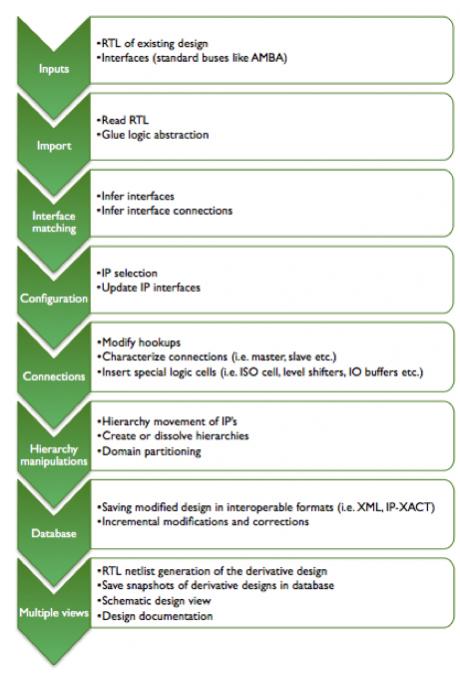

Atrenta’s GenSys is a tool that structures the whole process of doing derivative designs. It reads in an existing design in RTL (or a standard database like IP-XACT) to bring the design database into a new structured object model. This is a more reliable, flexible and just easier way to make changes according to a derivative design specification.

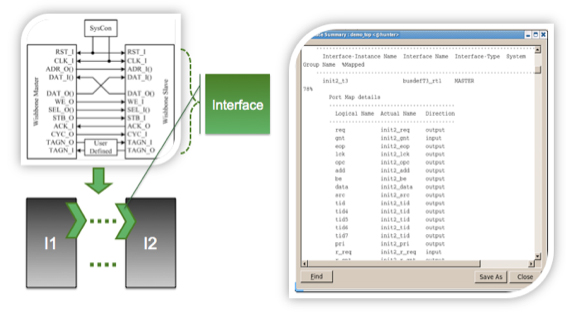

GenSys makes it easy to add, delete and update the existing IP blocks and their interfaces. Only a few clicks are required to remove a block or to update one. It also provides a very interactive way to build connections which can be used to update the existing connectivity with full transparency. Altering the hierarchy to group or ungroup blocks is also straightforward.

GenSys makes it easy to add, delete and update the existing IP blocks and their interfaces. Only a few clicks are required to remove a block or to update one. It also provides a very interactive way to build connections which can be used to update the existing connectivity with full transparency. Altering the hierarchy to group or ungroup blocks is also straightforward.

Taping out the design is also much easier. The design can be saved in interoperable formats such as IP-XACT or XML. The RTL netlist and schematics for the derivative design are then produced. The high level internal view means that it is simple to generate extensive design documentation.

GenSys is a framework for creating a derivative design while boosting productivity in terms of quick iterative cycles while eliminating errors in the design.

- Ease of data entry

- Fast design build time

- Ability to accept large modern designs

- Support for last-minute ECOs

- Automated generation of RTL netlist, design reports and documentation

- Customizable to support in-house methodologies

- Standard database backend allowing API-based access

GenSys has been used to tape out many chips at leading semiconductor companies. The GenSys white paper on derivatives is here.

Share this post via:

Solving the EDA tool fragmentation crisis