Memory designers need to predict the timing, current and power of their designs with high accuracy before tape-out to ensure that all the design goals will be met. Extracting the parasitic values from the IC layout and then running circuit simulation is a trusted methodology however the accuracy of the results ultimately depend… Read More

PQShield Demystifies Post-Quantum Cryptography with Leadership LoungePost-Quantum Cryptography, or PQC provides a technical approach…Read More

PQShield Demystifies Post-Quantum Cryptography with Leadership LoungePost-Quantum Cryptography, or PQC provides a technical approach…Read More Datacenter Chipmaker Achieves Power Reduction With proteanTecs AVS ProAs semiconductor technology advances and nodes continue to…Read More

Datacenter Chipmaker Achieves Power Reduction With proteanTecs AVS ProAs semiconductor technology advances and nodes continue to…Read More The Next LLM Architecture? Innovation in VerificationLLMs have amazing capabilities but inference run times…Read More

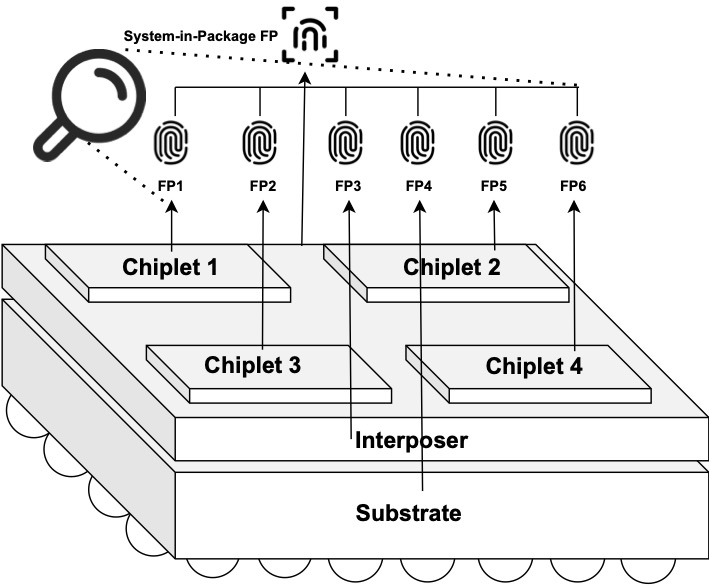

The Next LLM Architecture? Innovation in VerificationLLMs have amazing capabilities but inference run times…Read More Defect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRIIn the quest to secure the authenticity and…Read More

Defect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRIIn the quest to secure the authenticity and…Read MoreIntroducing TLMCentral

Way back in 1999 the open SystemC initiative (OSCI) was launched. In 2005 the IEEE standard for SystemC (IEEE1666-2005 if you are counting) was approved. In 2008, TLM 2.0 was standardized (transactional level models), making building virtual platforms using SystemC models easier. At least the models should be play nicely together,… Read More

Analog IP Design at Moortec

Stephen Crosher started up Moortec in the UK back in 2005 with the help of his former Zarlink co-workers and they set to work offering AMS design services and eventually created their own Analog IP like the temperature sensor shown below:

We spoke by phone last week about his start-up experience and how they approach AMS design.… Read More

Samsung versus Apple and TSMC!

Apple will purchase close to eightBILLION dollars in parts from Samsung for the iSeries of products this year alone, making Apple Samsung’s largest customer. Samsung is also Apple’s largest competitor and TSMC’s most viable competitive foundry threat so it was no surprise to see Apple and TSMC team up on the next generations of… Read More

Battle of the Patents

What’s going on in all these wireless patent battles? And why?

The first thing to understand is that implementing most (all?) wireless standards involves infringing on certain “essential patents.” The word “essential” means that if you meet the standard, you infringe the patent, there is no way around it. You can’t build a CDMA… Read More

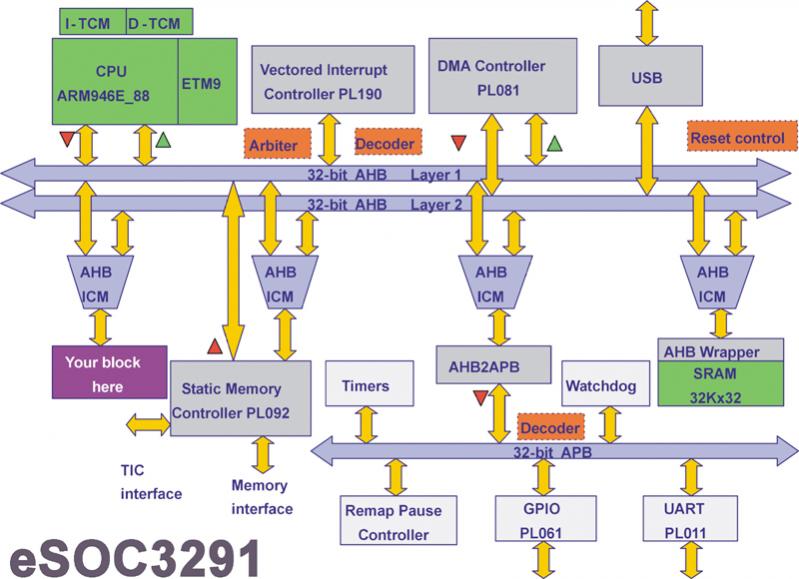

Magma eSilicon One Keynote

I was at the first half of Magma’s Silicon One event yesterday. The first keynote was by Rajeev about the environment for SoC designs, especially fabless startups, and Magma’s role going forward. More about that later. The other keynote was Jack Harding, CEO of eSilicon. As usual Jack did his presentation without … Read More

Cadence VIP Enables Users to be First-to-Market with Mobile Devices Leveraging Latest MIPI, LPDDR3 and USB 3.0 OTG Standards

The mobile devices market is simply exploding, with smartphones shipmentgoing up to the sky, tabletsemerging so fast that some people think it will replace PC (but this is still to be confirmed…). This lead mobile SoC designs to integrate increasingly more features, to support customer needs for more computing power and sophisticated… Read More

Apple Plays Saudi Arabia’s Role in the Semiconductor Market

The retirement of Steve Jobs left most commentators wondering if Tim Cook could lead Apple marching ever onward and upward. In truth, Tim Cook’s contribution on the operations side has been just as instrumental in the destruction of Apple’s PC and consumer electronics competitors as Jobs’ product vision. Under Tim Cook’s guidance,… Read More

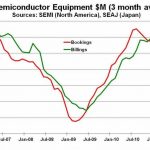

Semiconductor equipment spending beginning to decline

Semiconductor manufacturing equipment shipments have leveled off after a strong rebound from the 2008-2009 downturn. August 2011 three-month-average shipments based on combined data from SEMI (North American and European companies) and SEAJ (Japanese companies) were $2.9 billion, down from a peak of $3.2 billion in May … Read More

A Verilog Simulator Comparison

Intro

Mentor, Cadence and Synopsys all offer Verilog simulators, however when was the last time that you benchmarked your simulator against a tool from a smaller company?

I just heard from an RTL designer (who wants to remain anonymous) about his experience comparing a Verilog simulator called CVC from Tachyon against ModelSim… Read More

AI Semiconductor Market