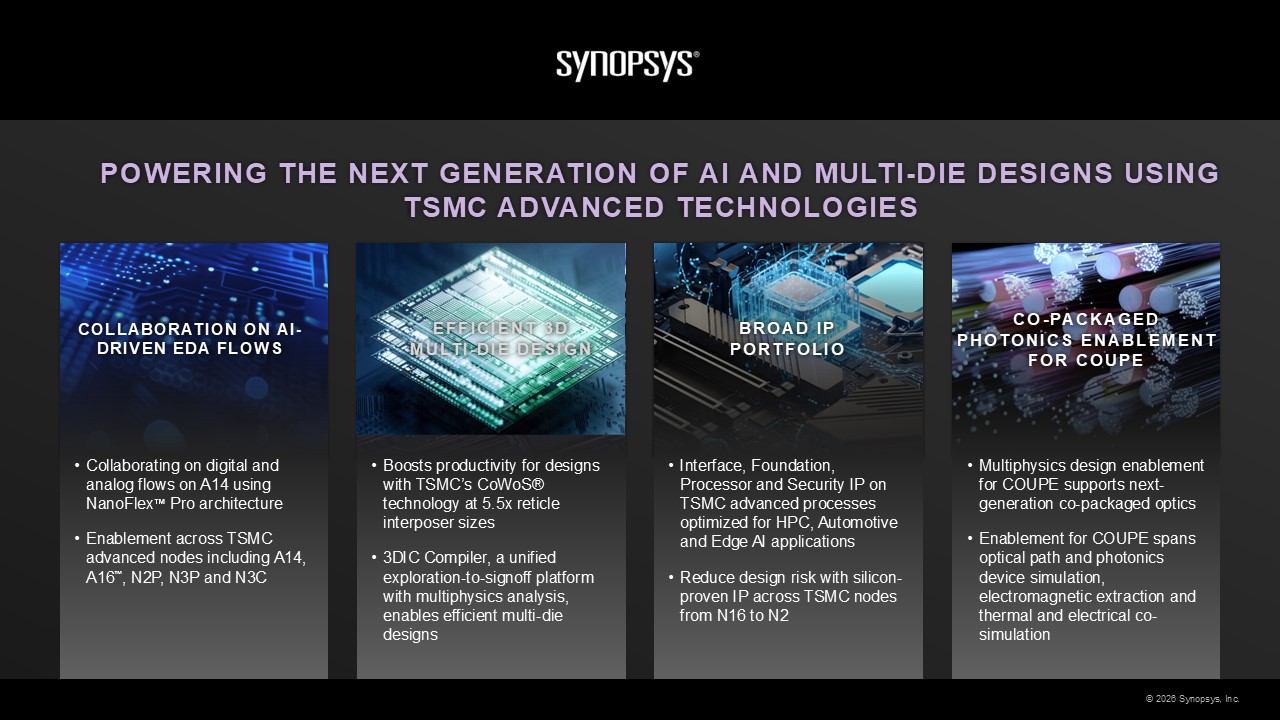

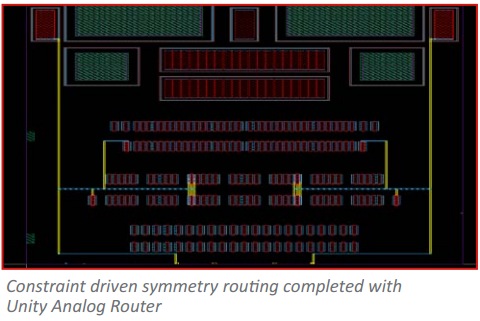

Earlier this week I wrote about a Goliath in EDA, Synopsys, and their new analog router, today it’s the David in EDA, Pulsic and their Unity Analog Router. I spoke with several people from Pulsic by phone:

- Christopher Jost – San Jose

- Dave Noble – San Jose

- Fumiaki Sato – Tokyo, Japan

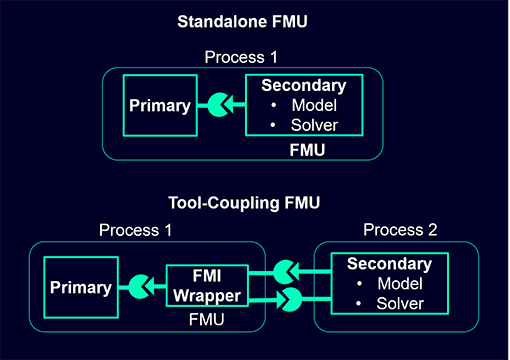

Siemens U2U 3D IC Design and Verification Panel