Yesterday evening was the annual EDAC CEO forecast meeting. Actually it is not really a forecast meeting any more, more a sort of CEO response to some survey questions asked of EDAC members. Rich Valera of Needham moderated with Lip-Bu, Aart and Wally, along with Simon Segars representing the IP arm(!) of the business and Raul Camposano… Read More

Reachability in Analog and AMS. Innovation in VerificationCan a combination of learning-based surrogate models plus…Read More

Reachability in Analog and AMS. Innovation in VerificationCan a combination of learning-based surrogate models plus…Read More Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural PivotIn 2003, legendary computer architect Michael J. Flynn…Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural PivotIn 2003, legendary computer architect Michael J. Flynn…Read More Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More

Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read MoreVisual Debugging at Altera on Billion-Transistor Chips

My first job out of college was doing transistor-level circuit design, so I’m always curious about how companies are doing billion-transistor chip design and debug these days at the FPGA companies.

I spoke with Yaron Kretchmer,he works at Altera and manages the engineering infrastructure group where they have a compute… Read More

Can “Less than Moore” FDSOI provides better ROI for Mobile IC?

In this previous article, I was suggesting that certain chip makers may take a serious look at a disruptive way to look at Moore’s law, as they may get better ROI, profit and even better revenue. The idea is to select technology node and packaging technique in order to optimize the Price, Performance, Power triptych and manage chip… Read More

Costello on Communicating a Compelling Company Story

The next EDAC sponsored emerging company series (what I’ve been calling Hogan University) is Joe Costello being interviewed on how to communicate a compelling company story. Anyone who saw Joe’s keynote at DAC several years ago will not want to miss this. I can’t promise that he’ll lie down on the stage… Read More

IJTAG for IP Test: a free seminar

What: Better IP Test with IJTAG

When: 26 March, 2013, 10:30am-1:30pm

Where: Mentor Graphics, 46871 Bayside Parkway, Fremont, CA 94538

If you are involved in IC test*, you’ve probably heard about the IEEE P1687 standard, called IJTAG for ‘internal’ JTAG. IJTAG defines a standard for embedded IP that includes simple… Read More

ARM Cortex SoC Prototyping Platform for Industrial Applications

If your next SoC uses an ARM Cortex-A9 and has an industrial application, then you can save much design and debug time by using a prototyping platform. The price to prototype is quite affordable, and the methodology has a short learning curve. Bill Tomasan Aldec Research Engineer conducted a webinar today on: ARM Cortex SoC Prototyping… Read More

Synopsys ♥ TSMC!

Dr. Paul McLellan and I will be covering the Silicon Valley SNUG live again this year. Unfortunately we are only allowed to see the keynotes (same thing with CDNLive) but they look very good:

Keynote Address: Massive Innovation and Collaboration into the “GigaScale” Age!

Aart de Geus, Chairman and co-CEO, Synopsys,… Read More

Will next generation Mobile Devices support PCI Express? M-PCIe is coming fast!

Those who have read the numerous articles I have written about MIPI, or PCIe, or the fusion of both named “Mobile Express” know my position: the question is not “Will Mobile devices support PCI Express?” but “When will we see Mobile devices integrating Mobile Express?” I was not really surprised by the Press Release that Cadence … Read More

Formal Verification of Power Intent

I can’t imagine that any SoC today is designed without taking intense interest in how much power the chip will consume, whether it is destined for a mobile phone or tethered in a cloud datacenter. One challenge with power is that adding features like voltage islands or power-down areas require changes to the netlist such as… Read More

Margaret Butler: One Woman’s Life in Science

46 years in Computing, 1945-1991

Margaret (Kampschaefer) Butler was a pioneer in technology, a ground-breaking woman who graduated with a B.S in Mathematics and Statistics in 1944, and followed a fascinating career path in the public sector starting in the earliest days of computers and nuclear energy. One of the early female… Read More

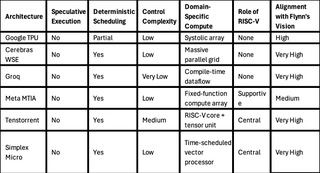

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot