Those who have read the numerous articles I have written about MIPI, or PCIe, or the fusion of both named “Mobile Express” know my position: the question is not “Will Mobile devices support PCI Express?” but “When will we see Mobile devices integrating Mobile Express?” I was not really surprised by the Press Release that Cadence has launched yesterday (07 March 2013), claiming the company support for Mobile PCIe Express (M-PCIe) solution, made of MIPI M-PHY IP, PCIe Controller IP and Verification IP for both, as MIPI M-PHY IP was part of Cosmic Circuit port-folio.

The surprise comes from the fast turnaround time between Cosmic Circuit acquisition and this announcement of M-PCIe support: exactly one month! If, like me, you hate the management posture which is to discuss forever before taking a decision, in fact discuss for such a long time that when the decision is taken it’s too late to get the entire benefit from the decision, you will appreciate this fast move, too!

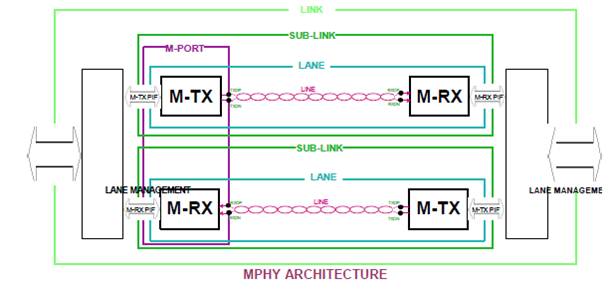

What exactly is Mobile Express specification? Just like extracting the best from the two protocols. PCI Express is a very complete (and complex) point to point interface protocol, offering many features (see at the bottom of this article for PCIe feature list) allowing optimizing chip to chip communication in various applications, but with a physical layer tending to be power hungry, when MIPI M-PHY has been specifically defined for mobile devices, targeting low power operation. According with Al Yanes, Chairman and President, PCI-SIG, “M-PCIe brings the necessary architecture to support advancement in tablets and smartphones as they take on the role of primary computing devices. The Mobile market is rapidly evolving and so are consumer expectations, placing an emphasis on low-power with increased performance for a better user experience.”

In fact, M-PCIe will allow chip makers and system developers, strong in PC segment, to re-use existing PCIe related architecture when moving to the various mobile segments. And MIPI Alliance clearly welcome PCIe related innovation: “The M-PCIe specification provides the Mobile industry with decades of innovation in PCIe technology coupled with the proven M-PHY physical layer that meets low-power requirements needed for today’s mobile device platforms,” said Joel Huloux, Chairman of the Board, MIPI Alliance.

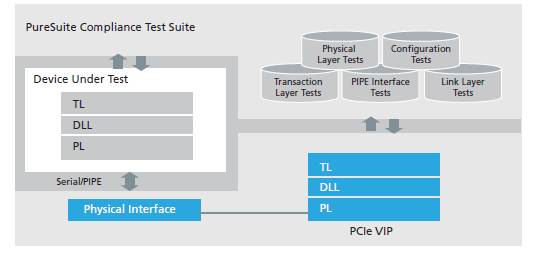

Existing PCIe Controller IP and Verification IP products and Cosmic Circuits acquisition allows cadence to bring a complete, integrated M-PCIe solution:

- MIPI M-PHY IP

- PCIe gen-3 Controller IP

- Verification IP for both M-PHY and PCIe controller

The readers familiar with the Interface IP market know that IP vendors able to support both pieces (Controller and PHY) get a competitive advantage over the competition: interoperability between these two parts has been validated by the vendor, and, for the buyer, the acquisition process is easier as he needs to interface with only one supplier, as well is the integration into the chip as the technical support comes from one source. And the same supplier providing Verification IP is also seen as a benefit, from the same reasons.

Because this announcement is very fresh, we don’t know yet what will be the operating frequency of M-PCIe solution which could be implemented today: PCIe gen-3 link operating frequency is specified at 8 Gbps, when M-PHY gear 3 specifications is 6 Gbps, which lead to an effective data rate of 4.8 Gbps due to 8B/10B encoding…

No doubt that we can rely on the cumulated energy of the MIPI Alliance contributor members to quickly figure out the best way using M-PCIe. I will let Joel Huloux, Chairman of the Board, MIPI Alliance, to conclude: “Mobile device users demand ever increasing power-efficiency and the MIPI Alliance chip-to-chip interfaces are an essential low power technology for smartphone and tablet developers. As an early contributing member of the MIPI Alliance, Cadence has helped speed the adoption of mobile specifications, now including the M-PHY-based M-PCIe”.

By Eric Esteve from IPNEST

Features

The PCIe core includes these features:

Single-Root I/O Virtualization

The PCIe core provides a Gen 3 16-lane architecture in full support of the latest Address Translation Service (ATS) specification, Single-Root I/O Virtualization (SR-IOV) specification, including Internal Error Reporting, ID Based Ordering, TLP Processing Hints (TPH), Optimized Buffer Flush/Fill (OBFF), Atomic Operations, Re-Sizable BAR, Extended TAG Enable, Dynamic Power Allocation (DPA, and Latency Tolerance Reporting (LTR). SR-IOV is an optional capability that can be used with PCIe 1.1, 2.0, and 3.0 configurations.

Dual-mode operation

Each instance of the core can be configured as an Endpoint (EP) or Root Complex (RC).

Power management

The core supports PCIe link power states L0, L0s and L1 with only the main power. With auxiliary power, it can support L2 and L3 states.

Interrupt support

The core supports all the three options for implementing interrupts in a PCIe device: Legacy, MSI and MSIx modes. In the Legacy mode, it communicates the assertion and de-assertion of interrupt conditions on the link using Assert and De-assert messages. In the MSI mode, the core signals interrupts by sending MSI messages upon the occurrence of interrupt conditions. In this mode, the core supports up to 32 interrupt vectors per function, with per-vector masking. Finally, in the MSI-X mode, the controller supports up to 2048 distinct interrupt vectors per function with per-vector masking.

Credit Management

The core performs all the link-layer credit management functions defined in the PCIe specifications. All credit parameters are configurable.

Configurable Flow-Control Updates

The core allows flow control updates from its receive side to be scheduled in a flexible manner, thus enabling the user to make tradeoffs between credit update frequency and its bandwidth overhead. Configurable registers control the scheduling of flow-control update DLLPs.

Replay Buffer

The Controller IP incorporates fully configurable link-layer reply buffers for each link designed for low latency and area. The core can maintain replay state for a configurable number of outstanding packets.

Host Interface

The datapath on the host interface is configurable to be 32, 64, 128 or 256-bits. It may be AXI or Host Application Layer (HAL) interface.

Comments

0 Replies to “Will next generation Mobile Devices support PCI Express? M-PCIe is coming fast!”

You must register or log in to view/post comments.