Internet of Things, or Internet of Everything, is certainly the buzzword of the year. Does IoT describe one product family? Not really as the acronym describes a family of concepts, each of these concepts could effectively be turned into a family of products, if this concept reach the market, or fulfill a market need. Nevertheless… Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

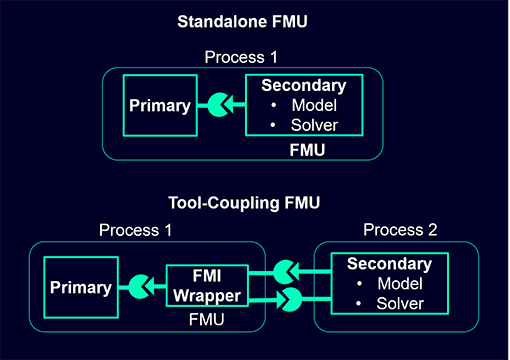

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read MoreA Brief History of ASTC and VLAB Works

When I worked for VaST our engineering was in Sydney Australia. To my surprise there was another, entirely independent, group working on virtual platform modeling and tools in another place in Australia, in Adelaide. Is there something in the Fosters? They had originally been part of Motorola Corporate R&D and Software Group,… Read More

ANSYS Electronics Simulation Expo – A View from Industry

As we are seeing more and more automation in most of our activities, not only through software but also smart electronics (at cutting-edge technologies) equipped with processors, micro-controllers, sensors and so on which make a whole system as an integrated entity on a small piece of semiconductor intertwined with other systems… Read More

eSilicon Creates One-Click Access to MPW and GDSII Quoting Portals

I have written before about eSilicon taking their internal quoting tool and making it user accessible. This first started just for MPW shuttles for half-a-dozen foundries, and then was extended to cover production runs at TSMC. And it is getting heavily used; eSilicon have had 315 people register to use it from 43 different countries… Read More

Virtual Platform Powers AUTOSAR Software Development

As a significant part of our life is spent in travelling, it’s natural that automotive sector continues to get traction with a significant push towards electronics and automated solutions for automobiles such as cars to provide safety, comfort and entertainment. These solutions are provided by complete systems which operate… Read More

Two New Announcements at ITC from Synopsys

Each year at the International Test Conference(ITC) we hear about the latest advances from the testability side of both EDA vendors and academics. This year Aart de Geus, Chairman and Co-CEO of Synopsys delivered a keynote speech titled, “Testing Positive, for Complexity“. Yesterday I spoke with Robert Ruiz and… Read More

SecureCore: secure MPU for IoT

The evaluation of the number of connected (IoT) systems by 2020 varies depending on the source, but we should see in the range of 30 billion IoT devices by that date. We already know some of the basic requirements: such a device will have to be connected, low cost, ultra-low power and… secure. The first three are key enablers, but we … Read More

SEMI Strategic Materials Conference and SEMICON Japan

I attended the SEMI Strategic Materials Conference earlier this month. I cover a pretty broad range of stuff on SemiWiki from embedded software and system-level design on down. But I usually stop at lithography and TCAD, which have a major impact on design and the whole fabless ecosystem. I hadn’t really thought about the… Read More

There’s good news about BadUSB

The good news about the recently-revealed BadUSB is that there actually is a cure: Hardware crypto engines were invented to protect software, firmware and hardware from exactly these types of attacks, among many others. These uber-tiny, ultra secure hardware devices can be easily and cost-effectively added to USB sticks (and… Read More

Crossfire on Continuous Path of Improvement

In an ever growing world of IPs, it’s essential that a tool which vouches to simplify designer’s job of IP development and help improving its quality remains versatile to encompass various formats, databases, common data models, standard libraries, scripting etc. that are used in the development of IPs and their exchange between… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!