Since pennants, drums, smoke, and horses fell out of favor to more advanced communication technology, network operators have struggled to find balance. Too few subscribers interested, and infrastructure investments completely fail. Just the right number of paying users, revenue streams provide profit and ability to invest… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreMentor Aims to Improve Yield and Production Ramp for PCBs

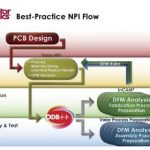

Getting a printed circuit board from design and into production presents one of the biggest challenges in successfully launching a product. The designer’s job is to anticipate issues that can adversely affect PCB fabrication and assembly. Design rules and component libraries go part of the way, but there is a thicket of things… Read More

Codasip and Coby and Czech

At ARM TechCon I ran into Coby Hanoch who has just been appointed VP worldwide sales of a comany that I’d not previously heard of called Codasip. As the name implies they supply code, and ASIPs. Well, actually IP source code and ASIP tools. The company is based in Brno (pronounced pretty much like Bruno) in the Czech republic … Read More

Leakage Current TCAD Calibration in a-Si TFTs

Two weeks ago I blogged about amorphous silicon and how that material is well-suited for designing TFTs. Today I’m following up after watching the archived webinarpresented by Nam-Kyun Tak of Silvaco. After clicking on that link you’ll be brought to a brief sign-up page and then can watch the archived webinar in your… Read More

More Apple A9 Ridiculousness!

File this one under funny things journalists are paid to say. Last week the Korea Times reported that Apple had “designated” Samsung as the primary supplier of the next Apple SoC. In response, the Chinese Commercial Times reported that TSMC is to supply the Apple A9 chip despite competition from Samsung. Since SemiWiki readers … Read More

Not Mobile, Automotive to See Max Semiconductor Growth!

There is no denying that mobile market is almost matured, the growth in the semiconductor industry has to pick up somewhere else. Although it’s expected that worldwide cellphone subscription will exceed the world population in 2015 (already exceeded in many parts of Europe) and continue for some time (while CAGR in unique subscription… Read More

Intel 2014 Investor Meeting and 14nm Status

Intel’s investor meeting was held yesterday and for me the presentation that is most interesting is Bill Holt’s. The presentations are available on the Intel website: Intel Corporation – Presentations Material 2014. Here is the 2013 version of this presentation: Intel Corporation – Presentations Materials 2013… Read More

ARMmbed? IoT dedicated ARM OS!

The IP vendor #1, leading the pack with revenues more than twice the closest competitor revenues, has to position on the new IoT market, especially because ARM’s main product line is processor IP family, and MCU or CPU is certainly at the earth of the SmarCoT: the “Smart” part. In fact, ARM’s customers have the freedom to develop any… Read More

Global Foundries and IBM, More Details

Now that the dust has started to settle on the GlobalFoundries acquisition of IBM’s semiconductor business it is possible to look into another level of detail about what GlobalFoundries will be acquiring in the way of technology and IP. Of course, the deal hasn’t formally closed yet so this won’t all happen … Read More

HLS Tools Coming into Limelight!

For about a decade I am looking forward to seeing more of system level design and verification including high level synthesis (HLS), virtual prototyping, and system modeling etc. to come in the main stream of SoC design. Although the progress has been slow, I see it accelerating as more and more tools address the typical pain points… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center