The joint development of 3D XPoint memory technology from Intel and Micron has once more brought the spotlight on data centers and chips for solid-state drives (SSDs). The two semiconductor industry giants claim that 3D XPoint memory is1,000 times faster than NAND Flash: the underlying memory content for SSDs. Such developments… Read More

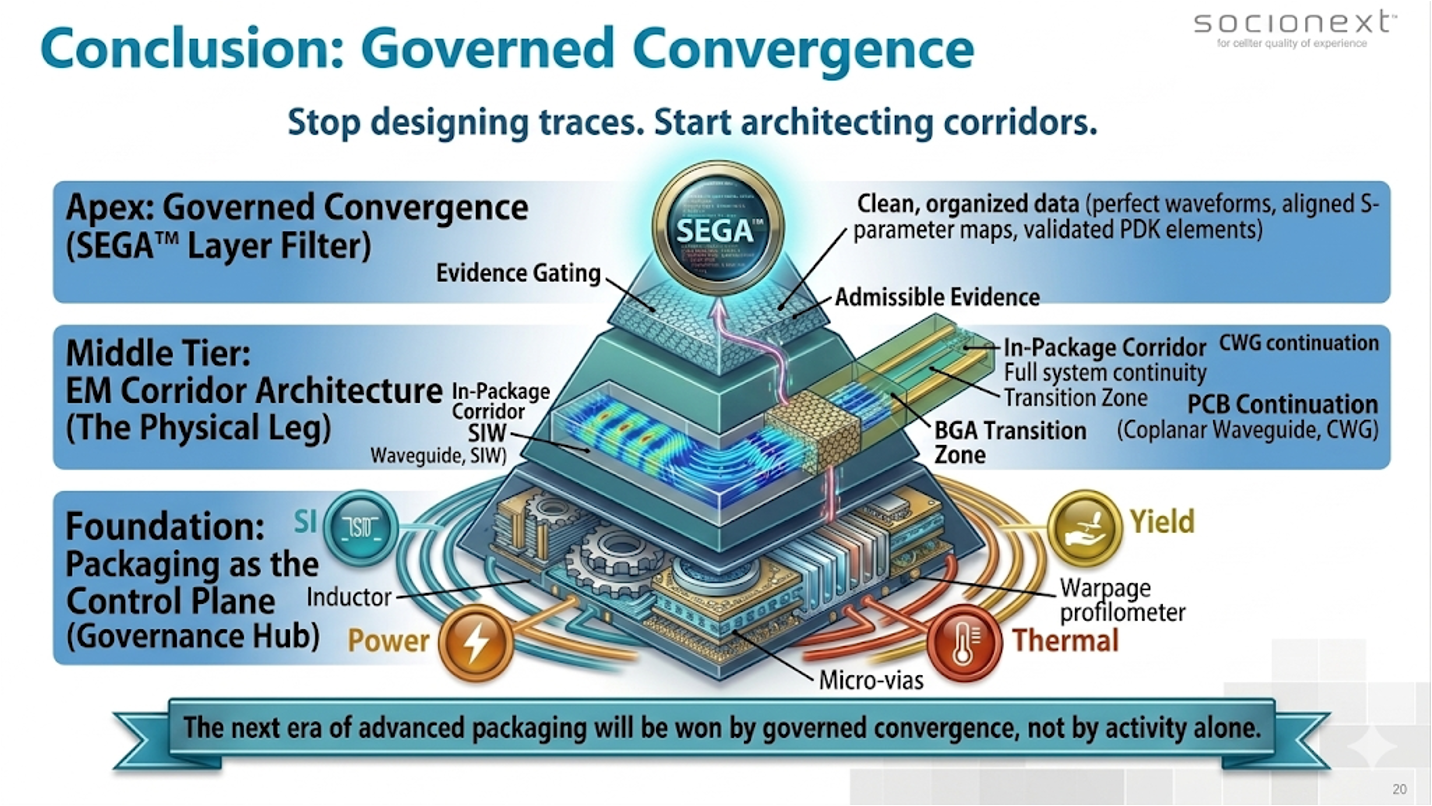

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

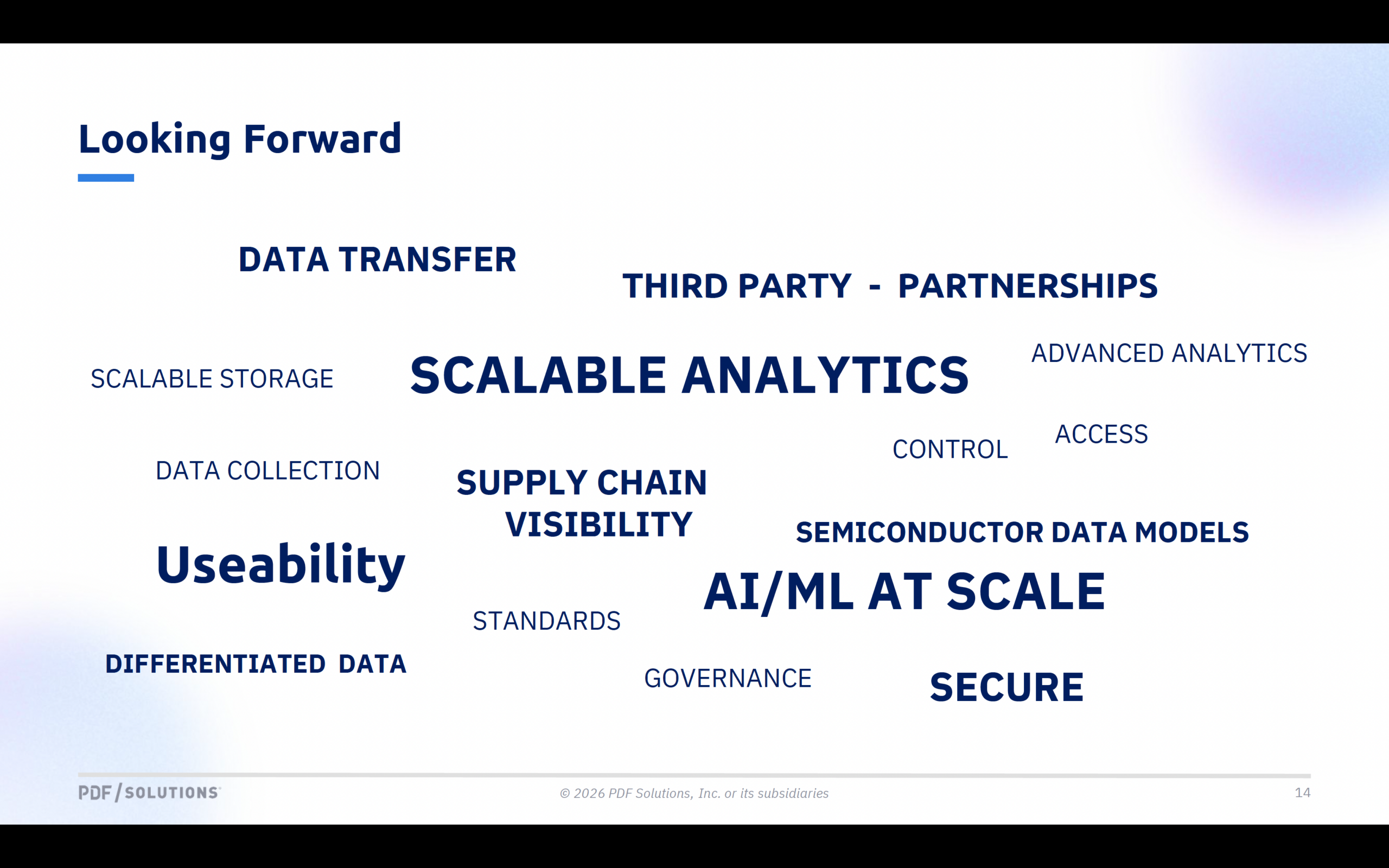

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read MoreI want to use USB Type C (and I want it now)

USB is certainly the most ubiquitous of the Interface protocols, used in our day to day life to connect multiple systems, as well as in professional segments like industrial or even high performance servers (yes, these systems integrates USB 3 connections). But USB is also one of the protocols able to generate frustration every… Read More

Silvaco 30 Years Ago

It’s Silvaco’s 30 year anniversary. You may already know the dry official story of the early days:

- Founded in 1984 by Dr Ivan Pesic

- In 1984 the initial product, Utmost, quickly became the industry standard for parameter extraction, device characterization and modeling.

- In 1985 Silvaco entered the SPICE circuit

ARM and the Law of Accelerating Returns!

ARM is one of the companies I have had professional experience with during my storied semiconductor career so I know some of their history first hand. I worked for a physical IP company that was purchased by ARM and at Virage Logic we competed against ARM head-to-head. ARM is also featured in our book “Fabless: The Transformation … Read More

A Key Aspect Missing for IoT to become NBT

The IoT (Internet of Things) is not one product, technology, segment, or market. It’s a combination of many things, many markets, and many technologies. However, it’s one thing that needs to connect everything together; edge device to gateway to cloud. That brings the complexity, how’s that possible amid large heaps of heterogeneous… Read More

Boost the Market for Interposer and 3D ICs with Assembly Design Kits

The traditional system-on-chip (SoC) design process has fully qualified verification methods embodied in the form of process design kits (PDKs). Why is it that chip design companies and assembly houses have no IC/package co-design sign-off verification process?

Package die are often produced using multiple processes and… Read More

Cadence 2015 Q2 Results

Let’s start by getting the financial stuff out of the way. Revenue was $416 million; non-GAAP operating margin was 28%; non-GAAP EPS was $0.27; and operating cash flow was $122 million (up at lot, it was just $47M in Q1 and $69M in Q2 of 2014).

The thing that the financial types are most interested in are the changes to Cadence’s… Read More

The Evolution of Smart Glass Design

The wearer says, “O.K., Glass” and glass leaps into action, performing most of the smartphone functions like check e-mails, take photos and videos, provide turn-by-turn navigation, and make and receive phone calls. Welcome to Smartphone 2.0.

Technology pundits called Google Glass the best thing that happened… Read More

The Antiportfolio

Last week Charlie Cheng of Kilopass wrote about venture capital for semiconductor. This reminded me of something amusing that I came across years ago.

See also VC For Semiconductor: Dead or Alive?

All VCs have a portfolio page and often a second exit page. The first shows the companies in which they currently hold investments and… Read More

UTBB SOI can scale down to 5nm says Skotnicki…

…and FinFET down to 3nm. This assertion is the result of extensive research work made by Thomas Skotnicki, ST Fellow and Technical VP, Disruptive Technologies, leading to numerous publications, like in 1988 in IEEE EDL or in 2008 in IEEE TED paper. I say extensive, I should also say long, very long, as it took almost 30 years for the… Read More

Is Intel About to Take Flight?