We boomers thought we would continue to innovate and live forever. We put men on the moon, we created rock and roll, we invented practical computers and personal computers, we did it all. And we lived the high life, especially in tech – big houses, fancy cars, great vacations. Then unexpectedly we got old (nobody warned us), and now… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreSix Ways Your Car Can Be Hacked!

The question is not IF but WHEN your car will be hacked. How about this: You connect your smartphone to your car and malware sets off the airbags. My car has front, side, and rear airbags so that would be a very painful and expensive experience for sure. According to my mechanic this is certainly possible and it would cost more than $10,000… Read More

ON to acquire Fairchild: pioneers join together

Last week ON Semiconductor announced it had agreed to acquire Fairchild Semiconductor for $2.4 billion. The combined company will be a major player in power analog and power discretes. It also combines two companies with ties to the beginning of the semiconductor industry.

Fairchild Semiconductor was founded in 1957 when eight… Read More

Power Reduction Verification Techniques Highlighted by Mentor at ARM Techcon

Power management is a perennial topic these days, and it came up in several presentations at the recent ARM Techcon in Santa Clara in mid November. The techniques covered in these talks address dynamic and static power consumption. The IEEE 1801 standard deals with specifying power design intent in Universal Power Format (UPF)… Read More

Finding under- and over-designed NoC links

When it comes to predicting SoC performance in the early stages of development, most designers rely on simulation. For network-on-chip (NoC) design, two important factors suggest that simulation by itself may no longer be sufficient in delivering an optimized design.

The first factor is use cases. I think I’ve told the story … Read More

USB Type-C opens doors for embedded system connectivity

Every now and then there is an innovation or advancement that changes the way we operate, the way the world operates. These innovations and advancements in technology creates opportunities for the businesses and provides improved features to the consumers. They are also widely and swiftly adopted. USB Type-C is one such technology… Read More

Smart Clothing: The Next Wave In Wearables

Today, it’s easier than ever to conceive a new product, prototype it, perfect it for mass production and successfully market it to an ever widening audience.

Accelerators and Incubators have sprouted up specifically to enable hardware startups and help them navigate the world of contract manufacturing and supply chain logistics.… Read More

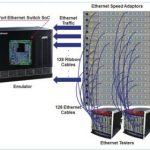

Networks, Emulation and the Cloud

To fans of Godel, Escher and Bach (the Eternal Golden Braid), there is an appealing self-referential elegance to the idea of verifying a network switch in a cloud-like resource somewhere on the corporate network. That elegance quickly evaporates however when you consider the practical realities of verifying such device in ICE… Read More

HLS with ARM and FPGA Technologies Boosts SoC Performance

The way SoC size and complexity are increasing; new ways of development and verification are also evolving with innovative automated tools and environment for SoC development and optimization. IP based SoC development methodology has proved to be the most efficient for large SoCs. This needs collaboration among multiple players… Read More

Intel 2015 Analyst Meeting Debunked!

Bill Holt’s “Advancing Moore’s Law” presentation at the recent Intel Analyst day was swallowed hook, line, and sinker by the mainstream media fish so let me play devil’s advocate here and point out some problems with his spin on the competitive landscape.

Coincidentally, one of my Intel friends insists that Intel is number one … Read More

Solving the EDA tool fragmentation crisis