The growth of the Internet of Things and embedded and wearable devices—will have widespread and beneficial effects by 2025. In all of these exponentially-growing technologies — artificial intelligence, robotics, nanomaterials, biotech, bioinformatics, quantum computing, Internet of everything — these … Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreExploring USB Type-C DRP to USB Type-C DFP connection using USB C-Thru

In a USB Type-C environment configuration process between a DRP and a DFP is as follows:

- DRP to DFP attach/detach detection

- Plug orientation detection

- Initial DRP to DFP and power relationship detection

- USB Type-C VBus current detection and usage

A Real Engineering Challenge – Artificial Red Blood Cells

When you’re thinking about “what can we do next”, you can think big or you can think small – very, very small. Robert Freitas at the Institute for Molecular Manufacturing (IMM) has such an idea – artificial red blood cells (RBCs). These would be nano-machines which could augment the oxygen and carbon dioxide carrying capacity of … Read More

The (not so) Easy Life of an SOC Design Integrator

How can large SOC projects effectively integrate sub blocks and IP into a stable version for release or internal development? The person responsible for integrating SOC sub blocks into a validated configuration for release has a difficult task. Usually there are many sub-blocks, each undergoing their own development. There… Read More

IoT implementation and Challenges!

The Internet of Things (IoT) is the network of physical objects—devices, vehicles, buildings and other items which are embedded with electronics, software, sensors, and network connectivity, which enables these objects to collect and exchange data. Implementing this concept is not an easy task by any measure for many reasons… Read More

DDR4 is a complex interface to verify — assistance needed!

The design of parallel interfaces is supposed to be (comparatively) easy — e.g., follow a few printed circuit board routing guidelines; pay attention to data/clock/strobe signal lengths and shielding; ensure good current return paths (avoid discontinuities); match the terminating resistances to the PCB trace impedance;… Read More

NHTSA and Google’s War on Drivers

Google and the National Highway Traffic Safety Admnistration (NHTSA) have recently joined forces in a battle against drivers. It is an unusual alliance and one with significant implications for the future of automotive safety in the U.S. and globally.

That alliance was manifest this week in a letter sent by NHTSA to Chris Urmson… Read More

Automotive Augmented Reality Applications Insights from Patents

US20150202962 illustrates a system for controlling vehicle features via an augmented reality vehicle user interface. The system includes an image capturing device for capturing an image of the vehicle. The system identifies the points of interest that correspond to the vehicle features within portions of the image of the vehicle… Read More

Does the Internet of Things need new Artificial Intelligence?

Judging by the number of confusing posts, blogs and articles on this topic, anyone exploring the potential of what the IOT can deliver to their business/organisation can be forgiven for thinking that the IOT will need a new set of AI technologies to work correctly. Throw into the mix the hype that the IOT will need big data analytics… Read More

Reconfigurable redefined with embedded FPGA core IP

On November 1, 1985, before anyone had heard the phrase field programmable gate array, Xilinx introduced what they called a “new class of ASIC” – the XC2064, with a whopping 1200 gates. Reconfigurable computing was born and thrived around the RAM-based FPGA, whose logic and input/output pins could be architected into a variety… Read More

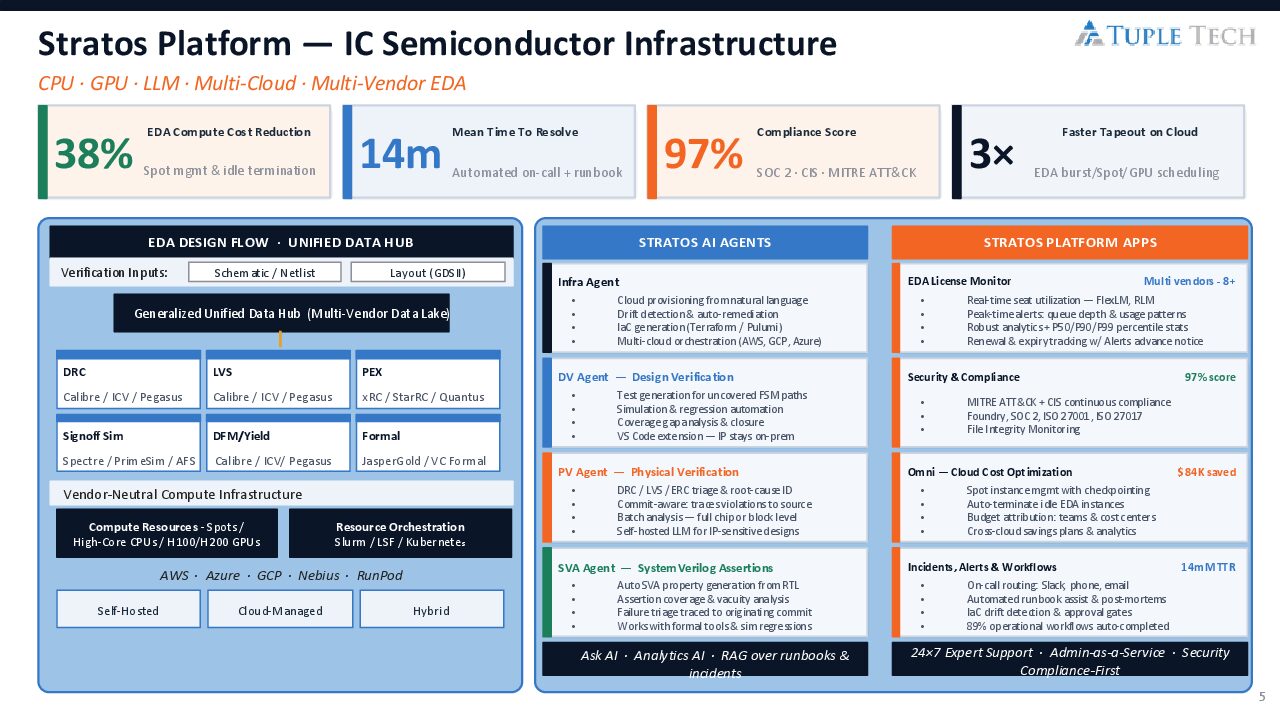

Solving the EDA tool fragmentation crisis