It’s funny that we all now believe that Google got the automated driving ball rolling. The reality is that the government started it all with the Defense Advanced Research Projects Agency (DARPA) and its famous DARPA Grand Challenge, which consisted of three tests (in 2004, 2005 and 2007) of driverless cars in different driving… Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More5 ways IoT can improve healthcare

The Internet of Things has applications that range all the way from automated manufacturing, to controlling the temperature of residential air conditioners. One particular area where IoT is hugely beneficial, is in the medical equipment industry.… Read More

VC Apps Tutorial at DVCon 2016

We might wish that all our design automation needs could be handled by pre-packaged vendor tool features available at the push of a button, but that never was and never will be the case. In the language of crass commercialism, there may be no broad market for those features, even though you consider that analysis absolutely essential.… Read More

You can see it if you look SXSW

Watching worlds of mobility, entertainment, and social media collide and helping customers navigate through this new technological landscape has been my passion for the last few years since I founded Left2MyOwnDevices. As a new arrival in Texas, I had my first chance to see just how big the convergence is at the premier event in… Read More

Why Can’t My Car be Like My iPhone?

Car companies must gaze with envy at Apple in the midst of its current confrontation with the Federal Bureau of Investigation in the U.S. over access to data on the iPhone of a terrorist. If only, they must say, if only we had Apple-like security for our cars.

By and large, when law enforcement agencies around the world need or want to… Read More

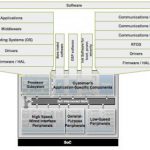

Can you really address the Automotive market with AP designed for smartphone?

If you remember, when TI decided to exit the booming wireless segment in 2012, the company decided to re-focus their application processor product line (OMAP) initially developed for smartphone “to a broader market including industrial clients like carmakers”. Being a TI employee in the 90’s in south of France, where TI has started… Read More

Attending DAC in Austin for Free

I love getting a good deal, and free is always compelling, so how about attending DAC in Austin for free this year? Sound too good to be true? Thanks to the generosity of three EDA companies – ATop Tech, ClioSoft and OneSpin, now you can can attend parts of DAC for free by registering here. This is now the 8th year that the I LOVE DAC… Read More

Software-Driven Verification and Portable Stimulus

I was at every single lunch at DVCon, not because the food was that great (it wasn’t bad) but because the topics were all interesting. The Wednesday lunch, hosted by Cadence, was a panel on software-driven verification and portable stimulus, moderated by Frank Schirrmeister (a different role for Frank – he’s usually a panel member… Read More

TSMC and ARM Serving up 7nm!

One thing I learned while writing the books about TSMC and ARM is that collaboration has always been at the core of both companies. They started with collaboration on day one and it is now a natural part of their business models. And the word collaboration in the fabless semiconductor ecosystem gets redefined at every process node,… Read More

SPIE – Interview with Greg Mcintyre of IMEC

One of the things I really like about major technical conferences is the opportunity to meet with people for networking and interviews. On Wednesday at the Advanced Lithography Conference I had the opportunity to interview Greg Mcinttyre, the director of advanced patterning at IMEC.

IMEC researchers are the first author on 32… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!