The definition of IoT systems is moving fast: the simple definition of a connected (to Internet) device in the early days is becoming more complex and also more precise. IoT or M2M devices are expected to support the full range of emerging cellular protocols such as LTE MTC Cat-1, Cat-0 or Cat-M, as well as the suite of Low Power Wide… Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

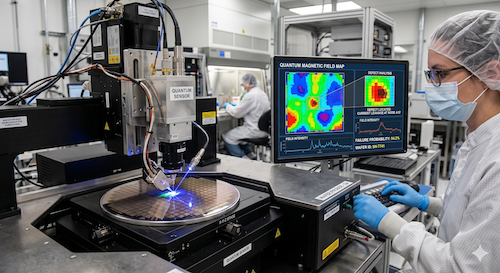

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read MoreSynaptics’ New Security Adapter Takes PC Fingerprint Security Literally Anywhere

Synaptics is an understated innovator in the human interface and end user experience technology space, and many of the hottest smartphones, tablets and PCs have their technology inside. The Samsung Galaxy S7, Apple iPhone 6S, Dell XPS 15, Microsoft Surface and Surface Book, and HP ENVY are just a few of these products I’ve personally… Read More

The Evolution of IoT Platforms

Hype-cycles are well known phenomena to those who pay attention to high-tech markets. Since we are probably at a peak of the early IoT hype-cycle in 2016, it’s natural to expect this latest wave of technologies to evolve just like other tech categories have in the past, with the eventual market power and market value going to a few … Read More

Democracy is a great thing, except in the workplace

“The Soviet Union I left behind was a dictatorship but the workplace was a democracy; America may be free but the workplace is a dictatorship” said Len Erlikh after I hired him at First Boston (now Credit Suisse First Boston) in 1986. Being of the Jewish faith, he had fled the U.S.S.R.’s religious persecution.

Erlikh’s words have … Read More

The iPhone 7 Intel Modem Controversy Explained!

The media is really having a field day on this one so I think it deserves further discussion. The rumor is that Intel has won the modem socket in the iPhone 7. The same rumor was circulating about Intel winning the modem socket for the iPhone 6 and the iPhone 5e so it really has reached urban legend status. The question I have is why does … Read More

AMD’s 7th Generation APU Brings Many Performance Tweaks And The Last Hurrah Before Zen

Advanced Micro Devices has already told us that 2016 was going to be the year of graphics, but the reality is that they also have a lot going on in their CPU and APU division as well. In fact, in addition to Advanced Micro Devices’s newly announced 7th Generation APUs in 2016, the company is also expected to launch their new Zen CPU cores… Read More

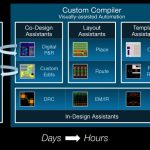

Custom IC Layout Design at #53DAC

Last week at the #53DAC conference there was a lot of excitement in the air about custom IC design, especially at the luncheon that I attended on Tuesday from Synopsys where they had customers like STMicroelectronics, GSI Technology, Samsung Foundry and the Synopsys IP group talk about their experiences using the new Custom Compiler… Read More

Design for the System Age

Of late, it has become painfully obvious that the value of electronics is in the system. And since systems demand continuing improvement, increasing performance and decreasing cost (once partially guaranteed by semiconductor process advances) is now sought through algorithm advances – witness the Google TPU and custom… Read More

IBM on the way back and still crazy about IOT

IBM Update: IOT Transformation on Track?

There have been some interesting developments for Big Blue in the IOT space recently. Last time we reported on them, we were monitoring analysts’ worries about the semiconductor business and other divestures late last year. This year, it seems clear IBM is poised to create even more profitable… Read More

The Business of the Semiconductor Business, Part One: What Happened?

This is the first of an occasional series of articles on the semiconductor industry. Many column inches have covered industry consolidation and in this first article, I aim to explain how the industry reached this point. Later articles will cover subjects including China, joint ventures, emerging players like Brazil and Vietnam,… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior