Telecom infrastructure is one area where X86 architecture hasn’t dominated historically. Infrastructure gear is spread across MIPS, Power, and SPARC architectures, with some X86, and a relative newcomer: ARM, already claiming 15% share. That’s a stunning figure considering only a bit less than 5 years ago… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreA Brief History of Platform Design Automation

Two weeks ago I spoke on the phone with Albert Li, Founder and CEO of Platform DA about his EDA company. Prior to founding Platform DA in Beijing, Li worked at Accelicon which was acquired by Agilent in December 2011. Mr. Li graduated from Tsinghua University and Vanderbilt University, both in Electrical Engineering, and has written… Read More

Brexit and Semiconductors

Interesting news last week with 51.9% of British voters saying yes to Brexit (exiting the European Union). What does it have to do with semiconductors? Plenty! After reading the media’s take on the subject and talking to friends (experts) in China, Taiwan, and Hong Kong, I must say that there is not a consensus to be found and there… Read More

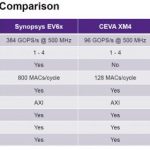

Synopsys Launch EV6x Vision Processor… Challenging the Competition!

When Synopsys bought Virage Logic in 2010, ARC processor IP was in the basket, but at that time ARC processor core was not the most powerful on the market, and by far. The launch of EV6x vision processor sounds like Synopsys has moved ARC processor core by several orders of magnitude in term of processing power. EV6x deliver up to 100X… Read More

Software Security is Necessary but NOT Sufficient

As the silicon designs inside the connected devices of the Internet of Things transition from specifications to tapeouts, electronics companies have come to the stark realization that software security is simply not adequate. Securing silicon is now a required, not optional, part of RTL design processes.… Read More

From Zero to IoT Prototype in One Month

The best things in life may not always be free, but they don’t have to be incredibly difficult to get to. A challenge for IoT designers has been that their bubbling excitement over the potential of their new gizmo is quickly tempered by the complexities of actually building the hardware. Not exactly what they have come to expect in … Read More

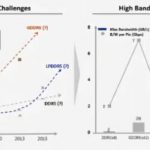

HBM controller IP holds the key to bandwidth

We were waiting to see what a different roster including SK Hynix and Synopsys would have to say on HBM in the latest Open Silicon webinar. This event focused on HBM bandwidth issues; a packaging session on 2.5D interposers was promised for a future webinar.… Read More

Circuit Simulation Panel Discussion at #53DAC

Four panelists from big-name semiconductor design companies spoke about their circuit simulation experiences at #53DAC in Austin this year, so I attended to learn more about SPICE and Fast SPICE circuit simulation. I heard from the following four companies:… Read More

High Level Synthesis Update

High-level synthesis (HLS) involves the generation of an RTL hardware model from a C/C++/SystemC description. The C code is typically referred to as abehavioraloralgorithmicmodel. The C language constructs and semantics available to architects enable efficient and concise coding – the code itself is smaller, easier to write/read,… Read More

Xilinx is Killing Altera!

At a recent outing with FPGA friends from days gone by, the long running Xilinx vs Altera debate has come to an end. The bottom line is that Xilinx has used the FUD (fear, uncertainty, and doubt) of the Intel acquisition quite effectively against Altera and is racking up 20nm and 16nm design wins at an alarming rate. It will be a while … Read More

ASML High-NA EUV is Not Ready for High-Volume Production