You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Anyone who travels long distances frequently is painfully familiar with this problem, but you may be wondering why I am mentioning it in this forum. The American Institute of Physics has a Chaos journal which looks at interdisciplinary problems in non-linear dynamics and recently published an article on just this topic.

There… Read More

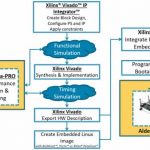

Designers tend to put tons of energy into pre-silicon verification of SoCs, with millions of dollars on the line if a piece of silicon fails due to a design flaw. Are programmable logic designers, particularly those working with an SoC such as the Xilinx Zynq, flirting with danger by not putting enough effort into verification?… Read More

Note: the table and text below have been revised from an earlier post to correct the numbers for STMicroelectronics.

Semiconductor companies posted a wide range of results in 2nd quarter 2016. Intel, Micron Technology and Renesas Electronics all had declines in revenue in 2Q 2016 versus 1Q 2016. Samsung Semiconductor, Qualcomm… Read More

Last June, the ESD Alliance (ESDA) has released Q1 2016 results for EDA (CAE, PCB & MCM and IC Physical), Silicon IP (SIP) and Services. Not a surprise for Semiwiki readers since 2013, the SIP category is recognized as the largest with $689 million revenues for the quarter, and four-quarters moving average increasing by 11.6… Read More

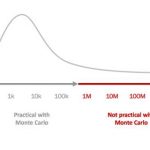

When pushing the boundaries of power and performance in leading edge memory designs, yield is always an issue. The only way to ensure that memory chips will yield is through aggressive simulation, especially at process corners to predict the effects of variation. In a recent video posted on the Solido website, John Barth of Invecas… Read More

SoC designers can now capture their design ideas with high-level languages like C and SystemC, then synthesize those abstractions down into RTL code or gates, however in the end the physical IC is implemented using cell libraries made up of transistors. Circuit designers use simulation tools like SPICE on these transistor-level… Read More

Neural nets are a hot topic these days and encourage us to think of solutions to complex tasks like image recognition in terms of how the human brain handles that task. But our model today for this neuromorphic computing is several steps removed from how neurons actually work. We’re still using conventional digital computation … Read More

What happens when you get a panel of four executives together with an industry-leading journalist to discuss tradeoffs in IoT designs? After the obligatory introductions, Ed Sperling took this group into questions on power, performance, and integration.… Read More

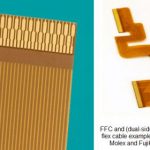

The three F’s of electronic product development are: form, fit, and function. Although the F/F/F assessment typically refers to the selection of the right component, it most definitely also refers to the selection of the proper cabling between assemblies. The requirements for cables are varied, and demanding: ability… Read More

I’ve owned and used many generations of cell phones, starting back in the 1980’s with the Motorola DynaTAC phone and the biggest usability factor has always been the battery life, just how many hours of standby time will this phone provide and how many minutes of actual talk time before the battery needs to be recharged… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry