When Charlie Janac talks, people listen, absolutely. Charlie’s 30 year career spans EDA, IP, semiconductor equipment, nano-technology, and venture capital. For the last 11 years he has been CEO of interconnect IP provider Arteris who invented the industry’s first commercial network on chip (NoC) SoC interconnect IP… Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

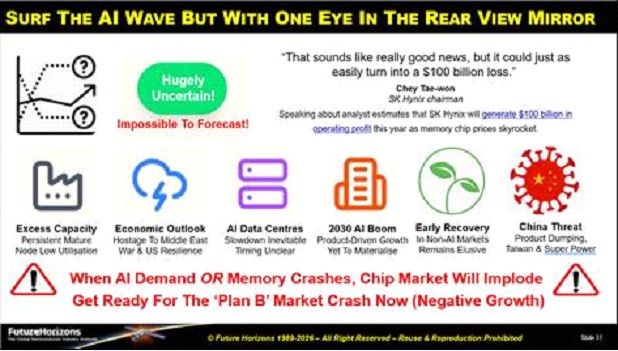

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MoreVidyo Aims To Disrupt Video Banking After Seeing Success In Healthcare And Defense

Commercial video services are a funny thing- they seem to go through ebbs and flows of industry excitement. One day it seems boring and the next thing you see is live video from a drone, Google releasing Duo, a patient traveling on a dogsled to receive care from a doctor a 1,000 miles away… and then everyone gets excited again. I worked… Read More

The Secret Plans of Mark Rosekind & Donald Trump

Donald Trump says he has a secret plan for defeating ISIS in Syria, but says it would be self-defeating to share that plan with the American electorate and, presumably, ISIS itself. Administrator Mark Rosekind says the National Highway Traffic Safety Administration has a plan for reducing highway fatalities to zero in the U.S.,… Read More

5 Best Practices For Developing Secure IoT Solutions

Security is often an afterthought when developing IoT solutions. Security features are commonly cut from initial designs to accommodate additional device functionality. However, security needs to play a central role in IoT projects if we are to secure the Internet of Things.

The process of developing secure IoT solutions was… Read More

Adding DSP hardware shrinks energy for MCU core

ARM’s Cortex-M4 processor core represented quite a breakthrough in digital signal controller technology when launched in 2010. Adding a single-cycle multiplier and SIMD instructions enabled basic DSP algorithms while retaining the low power benefits of an MCU. New technology circa 2016 – embedded programmable logic – can… Read More

Semiconductor C-level Executives Explore the Seventh Sense!

The GSA US Executive Forum is in its 5[SUP]th[/SUP] year. It is a time for top level semiconductor executives to meet and try to make sense of a very complex and fast moving industry that has tremendous influence on modern day life. You can see a list of attendees with bios and pictures HERE. There is a lot to talk about (The Future of Drones… Read More

eSilicon Just Made It Easier to Explore Memory Tradeoffs

If you are building an advanced SoC, you know that you’re going to need a lot of embedded memory. Unless this is your first rodeo, you also know that which memories you choose can have a huge impact on Power, Performance and Area (PPA) and, for some applications, Energy (power integrated over time), Temperature and Reliability. Which… Read More

Circuit Simulation Videos Show How To

One of the things that I miss most about attending trade shows like DAC in the old days was that you actually got to see EDA tools being demonstrated live in the exhibit area. You could see what the GUI looked like, how the dialogs worked, and learn what kind of control you could have during analysis. Most of what you see today at DAC in the… Read More

CEO Interview: Marie Semeria of LETI

Laboratoire d’électronique des technologies de l’information (LETI) is a French research center, affiliate to the CEA (Commisariat a l’Energie Atomique). Since LETI creation in 1967, this affiliation has two consequences, the money was flowing from the deep pocket of the atomic industry to sustain advanced … Read More

Machine Learning – Turning Up the Sizzle in EDA

There’s always a lot of activity in EDA to innovate and refine specialized algorithms in functional modeling, implementation, verification and many other aspects of design automation. But when Google, Facebook, Amazon, IBM and Microsoft are pushing AI, deep learning, Big Data and cloud technologies, it can be hard not to see… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior