I spent the last several days doing a deep dive into the world of IoT security and what I’ve learned has scared the pants off me. Various analysts predict that there will be over 30 billion connected IoT devices by the year 2020 growing from 9.9 million in 2013. A quick audit of my home identified over 40 connected devices including everything… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreHow ARM designs and optimizes SoCs for low-power

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

CEO Interview: Dündar Dumlugöl of Magwel

Magwel CEO Dündar Dumlugöl is well known from his days at Cadence, where I first met him, and for his more recent tenure at Magwel. At Cadence he led the team that first developed Spectre. He has come a long way from the start of his career at IMEC in Belgium. He and I had a chance to have a conversation recently where he offered insights … Read More

Building a Solar Powered Ice Freezer

My vacation is your worst nightmare. Well, at least that is what the bumper sticker says – it’s referring to Burning Man. It’s well known that among the tens of thousands of people attending this arts festival in Nevada at the end of each Summer there are lots of high tech luminaries. I also have gone many times – not to say that I am a luminary.… Read More

Top IOT News for 2016

2016 will go down as being part of the golden era for the Internet of things. This last year has experienced incredible advancements like cars that drive themselves, and cities that actually smarter. It has also been a learning experience where major security breaches threatened us, but we worked past them, and ultimately built… Read More

Mind-Boggling Uber Hubris

Uber was on a mighty roll throughout 2016 picking up strategic alliances with Ford Motor Company and Volvo Cars (for test vehicles) adding talent (cybersecurity experts Chris Vlasek and Charlie Miller) and acquisitions (Otto) and rubbing up against university researchers (Carnegie Mellon). So it was jaw-droppingly hideous… Read More

IEDM 2016 – 7nm Shootout

In the first session of IEDM on Monday, December 5th there were two papers presented on 7nm processes. The first paper was from TSMC and the second paper was from the Global Alliance of GLOBALFOUNDRIES, IBM and Samsung.… Read More

IEDM 2016 – GLOBALFOUNDRIES 22FDX Update

At IEDM in 2015 I had a chance to sit down with Subramani (Subi) Kengeri and get a briefing on GLOBALFOUNDRIES 22FDX technology. At IEDM 2016 Rick Carter of GLOBALFOUNDRIES presented a paper on 22FDX. Following Rick’s presentation, I had a chance to sit down with Rick and John Pellerin, VP of Technology and Integration and … Read More

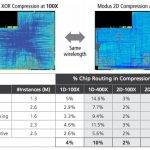

Reducing the Cost of SoC Testing

Every year certain technology themes appear, like at ITC this year a big theme was how to reduce the cost of SoC testing. I spoke with Rob Knoth of Cadence by phone to hear more about this cost of test theme. Rob gave me an example of an SoC that takes 27 seconds on a tester, so at $0.04 per second in test costs amounts to $1.08 per part. If you… Read More

Enter the Cellular IoT

You could be forgiven for thinking that wireless in an IoT device must be Bluetooth-5 or Zigbee or Thread. After all, that’s what ARM has introduced as a part of their IoT solution and they have market weight that is difficult to dismiss. However those options aren’t the only game in town. There is already some level of (second… Read More

ASML High-NA EUV is Not Ready for High-Volume Production