The Cadence Tensilica DNA100 DSP IP core is not a one-size-fits-all device. But it’s highly modular in order to support AI processing at the edge, delivering from 0.5 TMAC for on-device IoT up to 10s or 100 TMACs to support autonomous vehicle (ADAS). If you remember the first talks about IoT and Cloud, a couple of years ago, the IoT … Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More yieldHUB Expands Its Impact with New Technology and a New WebsiteyieldHUB is a unique company that focuses on…Read More

yieldHUB Expands Its Impact with New Technology and a New WebsiteyieldHUB is a unique company that focuses on…Read More Architecting Intelligence: The Rise of RISC-V CPUs in Agentic AI InfrastructureSiFive’s newly announced $400 million Series G financing…Read More

Architecting Intelligence: The Rise of RISC-V CPUs in Agentic AI InfrastructureSiFive’s newly announced $400 million Series G financing…Read More Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed SeaIntel, Musk, and the Tweet That Launched a…Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed SeaIntel, Musk, and the Tweet That Launched a…Read MoreMore Negative Semiconductor News

The amount of negative news and information about the semiconductor industry seems to be increasing at a faster rate. Micron put up a better quarter than expected but more importantly guided less than expected. We are surprised that the street is surprised as the decline in memory pricing is well known and Micron has been clear about… Read More

Neural Network Efficiency with Embedded FPGA’s

The traditional metrics for evaluating IP are performance, power, and area, commonly abbreviated as PPA. Viewed independently, PPA measures can be difficult to assess. As an example, design constraints that are purely based on performance, without concern for the associated power dissipation and circuit area, are increasingly… Read More

Systems Design vs Integrated Circuit Design

This is the sixteenth in the series of “20 Questions with Wally Rhines”

Electronic design automation (EDA) began and grew with the integrated circuit (IC) design business probably because IC design grew in complexity faster than printed circuit boards. The race for superiority in PCB design evolved in parallel,… Read More

Apogee Pipelining in Real Time

Pipelining exploits parallelism of sub-processes with intent to achieve a performance gain that otherwise is not possible. A design technique initially embraced at the CPU micro-architectural level, it is achieved by overlapping the execution of previously segregated processor instructions –commonly referred … Read More

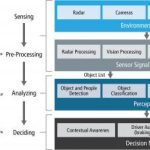

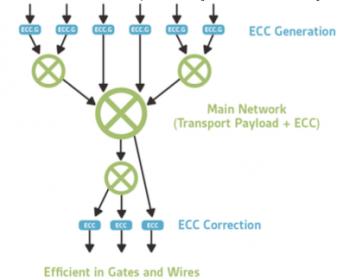

Supporting ASIL-D Through Your Network on Chip

The ISO 26262 standard defines four Automotive Safety Integrity Levels (ASILs), from A to D, technically measures of risk rather than safety mechanisms, of which ASIL-D is the highest. ASIL-D represents a failure potentially causing severe or fatal injury in a reasonably common situation over which the driver has little control.… Read More

Semiconductor IP Reality Check

A robust, proven library of IP is a critical enabler for the entire semiconductor ecosystem. Without it, ASIC design is pretty much impossible, given time-to-market pressures. Said another way, designing IP for your next chip simply doesn’t fit the schedule – most teams have barely enough time to integrate and validate pre-existing… Read More

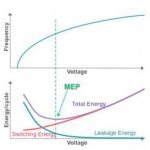

Integrated Power Management IP to Decrease Power and Cost

This blog is the synthesis of a white paper “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, which can be found on Dolphin Integration web site.

The power consumption generated by complex chips was not a real issue when the system could be simply plugged in the wall to … Read More

Beyond DRC and LVS, why Reliability Verification is used by Foundries

Reliability of ICs isn’t a new thing, because back in 1980 I was investigating why a DRAM chip using 6um technology was having yield loss due to electromigration effects. I recall looking through a microscope at a DRAM layout and slowly ramping up the Vdd level then suddenly the shiny aluminum interconnect started to change… Read More

Webinar: Multicycle Vectorless Dynamic IR Signoff for Near 100 Percent Coverage

Check this webinar out – Mediatek will share a novel approach to early IR drop estimation. Competition in system design has become even more intense because potential markets are huge and there are more players with deep pockets chasing those markets. Wherever you are in those value chains, you want to shift everything left to accelerate… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea