SLAM – simultaneous localization and mapping – is critical for mobile robotics and VR/AR headsets among other applications, all of which typically operate indoors where GPS or inertial measurement units are either ineffective or insufficiently accurate. SLAM is a chicken and egg problem in which the system needs to map its environment… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More#56DAC – Machine Learning and its impact on the Digital Design Engineer

Tuesday for lunch at #56DAC I caught up to the AI/ML experts at the panel discussion hosted by Cadence. Our moderator was the affable and knowledgable Prof. Andrew Kahng from UC San Diego. Attendance was good, and interest was quite high as measured by the number of audience questions. I learned that EDA tools that use heuristics… Read More

#56DAC – Panel Discussion: Closing Analog and Mixed-Signal Verification in 5G, HPC and Automotive

Monday afternoon at #56DAC I enjoyed attending a luncheon panel discussion from four AMS experts and moderator, Prof. Georges Gielen, KU Leuven. I follow all things SPICE and this seemed like a great place to get a front-row seat about the challenges that only a SPICE circuit simulator can address. Here’s a brief introduction… Read More

Cadence Releases Enterprise-Level FPGA Prototyping

Big prototyping hardware is essential to modern firmware and software development for pre-silicon, multi-billion gate hardware. For hardware verification it complements emulation, running fast enough for realistic testing on big software loads while still allowing fast-switch to emulation for more detailed debug where… Read More

2020 57thDAC to Co-Locate with SEMICON West!

Probably the most interesting news out of 56thDAC thus far is the announcement that in 2020 and 2021 DAC will co-locate with SEMICON West. It’s great news really since this is something that has been discussed over the years but has been deadlocked due to “failed negotiations”. Unfortunately, simple logic goes out the window with… Read More

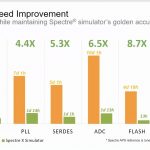

Parallel SPICE Circuit Simulator Debuts

In EDA the most successful companies will often re-write their software tools in order to add new features, improve accuracy, increase capacity and of course, shorten run times. For SPICE circuit simulators we typically look at several factors to see if a new tool is worth a look or not:

- Netlist compatibility

- Model support

- Foundry

A Practical Approach to Modeling ESD Protection Devices for Circuit Simulation

Lurking inside of every Mosfet is a parasitic bipolar junction transistor (BJT). Of course, in normal circuit operation the BJT does not play a role in the device operation. Accordingly, SPICE models for Mosfets do not behave well when the BJT is triggered. However, these models work just fine for most purposes. The one important… Read More

The Genius Sperm Bank

The “20 Questions with John East” series continues

How did it happen? How did Fairchild transform over a decade into the “off with their heads” culture? To understand that, you need to know a little about the William Shockley story. William Shockley was born in London in 1910. He moved to Silicon Valley when he was 3. Of course,… Read More

Needham is Upbeat about EDA and IP Growth at #56DAC

It’s Sunday afternoon and I just attended the annual Needham presentation at #56DAC in sunny Las Vegas, where Rich Valera shared an upbeat view of EDA and IP growth. Here are the five drivers of this growth:

- IoT

- Automotive

- Webscale/FAANGs

- AI/ML

- China

For the IoT market they’ve seen a CAGR of 8.6% to $8.2B in 2018, projected… Read More

In Their Own Words: TSMC and Open Innovation Platform

TSMC, the largest and most influential pure-play foundry, has many fascinating stories to tell. In this section, TSMC covers some of their basic history, and explains how creating an ecosystem of partners has been key to their success, and to the growth of the semiconductor industry.

The history of TSMC and its Open Innovation … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry