In July, I explored the benefits of the new Cadence Tempus™ Power Integrity Solution. In that piece, I explored some of the unique capabilities of this new tool with Brandon Bautz, senior product management group director and Hitendra Divecha, product management director in the Digital & Signoff Group at Cadence. I recently… Read More

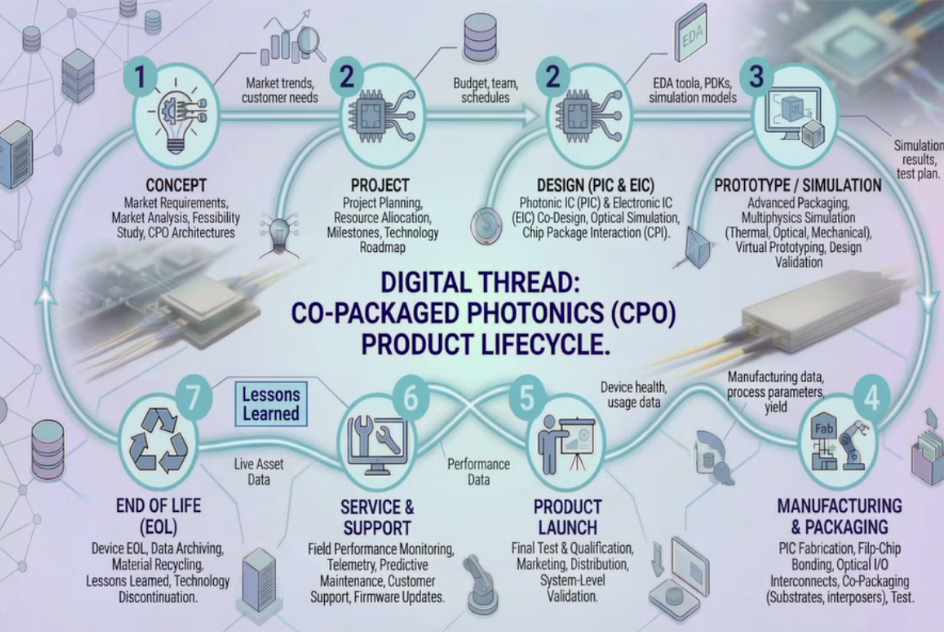

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More

RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read MoreVerification IP Coverage

I am pleased to introduce Truechip to the SemiWiki community. Truechip is a leader in the IP Verification – Design and Verification solutions market, one of the fastest growing market segments we track. Truechip has been serving customers for more than 10 years specialization in VIP integration, customization and SOC Verification.… Read More

Toshiba Cost Model for 3D NAND

Toshiba (now known as Kioxia) was the first company to propose a 3D stacked version of NAND Flash memory called BICS [1]. BICS (BIt Cost Scalable) Flash used explicit process cost reduction based on depositing and etching multiple layers at once, avoiding multiple lithography steps. This strategy replaced the usual approach… Read More

Like US and China, India must ensure foreign tech companies are locally owned

Synopsis: India could learn from both countries, requiring that Facebook India be sold to one of India’s tech tycoons. This would be one step to ensuring that all data be kept locally and tightly protected, and that the algorithms that determine the information that users will receive – which, after all, influences their behaviour… Read More

Three Things You Have Wrong About Intel!

First let me tell you that I have nothing but respect for Intel. I grew up with them in Silicon Valley and have experienced firsthand their brilliance and the many contributions they have made to the semiconductor industry. In fact, I can easily say the semiconductor ecosystem would not be what it is today without Intel.

But no company… Read More

CEO Interview: Wally Rhines of Cornami

Wally Rhines is President and CEO of Cornami, Inc., a company named for its “tsunami of cores”. The company has developed a “TruStream” programming environment that generates independent executable streams of data and control. They have also designed a chip that provides the computational fabric for multi-core execution of… Read More

yieldHUB – A Yield Management Checklist for Startups and a New Look

In July, I covered a webinar that described how yieldHUB helps bring a new product to market. That webinar described how to implement new production introduction (NPI) using an array of tools and techniques that should be part of any semiconductor enterprise. In a recent article published by yieldHUB, they took a few steps back … Read More

Arm Mobility and Industrial Advances in Safety, Flexibility

Again on the theme of rationalizing NVIDIA’s $40B acquisition of Arm, two more hot areas for growth are mobility and industrial automation markets. NVIDIA is already strong in intelligent mobility and Arm is is virtually everywhere in the modern car. Ditto for robotics in industry. In fact the two domains have significant overlap:… Read More

Apple Is Evaluating Scratch Resistant Diamond Like Coatings On Gorilla Glass

Despite the improvements in glass material used in smartphone displays, many, if not all, leading smartphone manufactures such as Apple and other smartphone manufacturers are evaluating a coating method that further increases the durability of screens at a cost of just pennies per display by coating them with diamonds.… Read More

Digital Design Technology Symposium!

Synopsys virtual events are high on my list for three reasons:

- They are very well organized and professionally

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea