The performance demands of data centers continue to grow, driven to large degree by the ubiquitous use of complex AI algorithms. On April 25, Embedded Computing Design held an informative webinar on this topic. Two experts looked at the problem from the standpoint of processor architecture and communication strategies, which… Read More

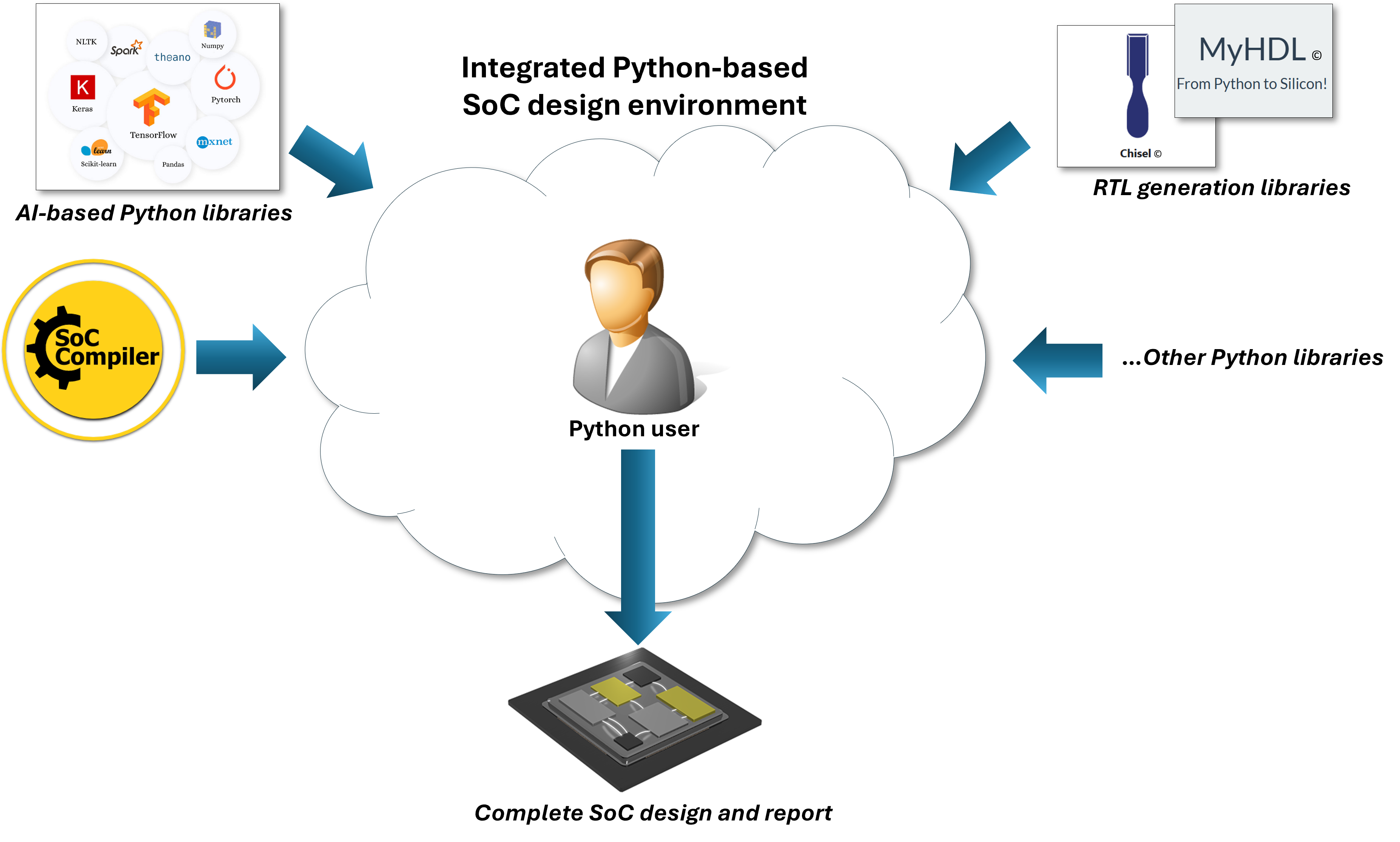

Build a 100% Python-based Design environment for Large SoC DesignsIn the fast-evolving world of semiconductor design, chip…Read More

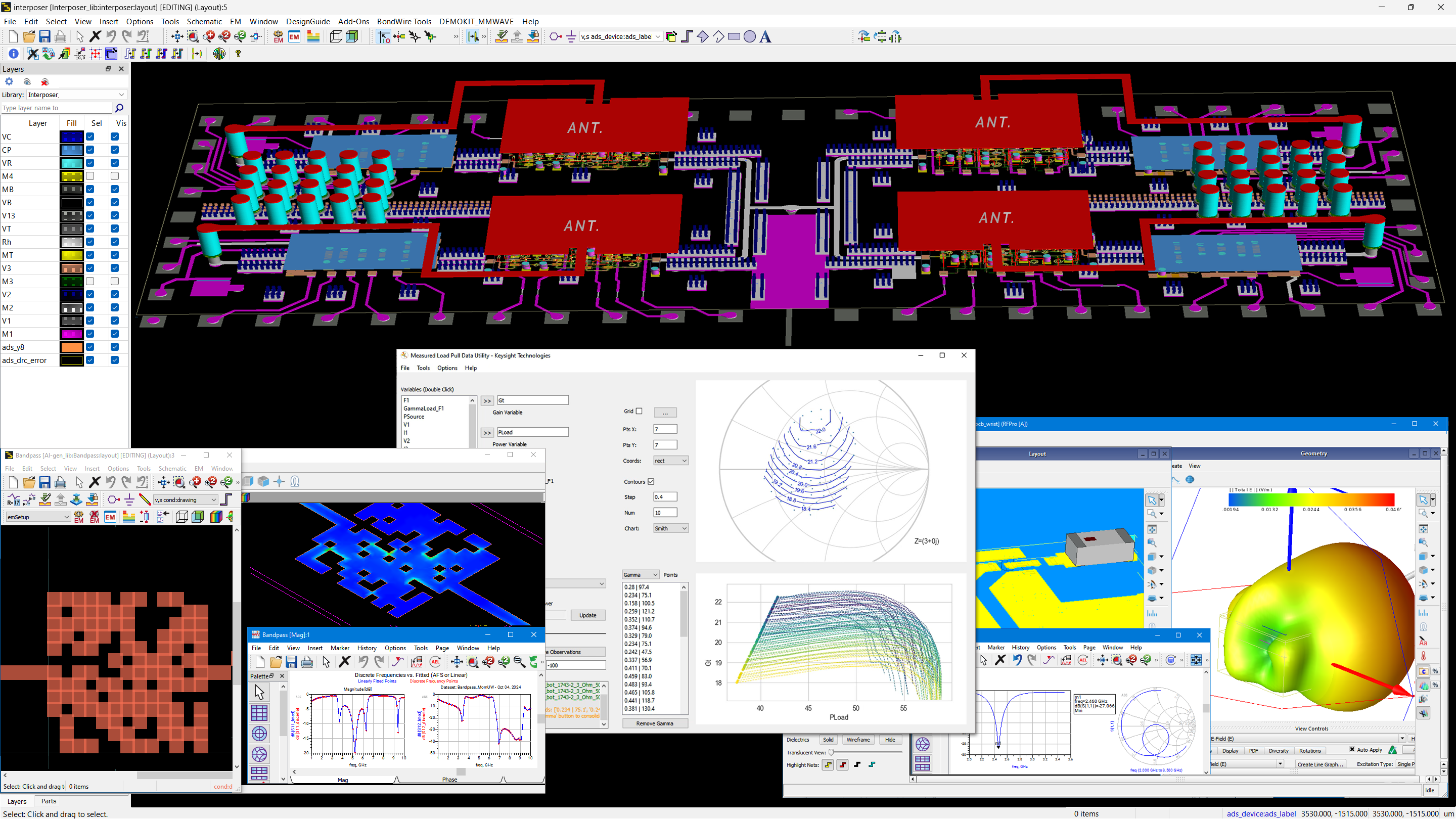

Build a 100% Python-based Design environment for Large SoC DesignsIn the fast-evolving world of semiconductor design, chip…Read More Keysight EDA 2025 launches AI-enhanced design workflowsThe upcoming Keysight EDA 2025 launch has three…Read More

Keysight EDA 2025 launches AI-enhanced design workflowsThe upcoming Keysight EDA 2025 launch has three…Read More Changing RISC-V Verification Requirements, Standardization, InfrastructureA lively panel discussion about RISC-V and open-source…Read More

Changing RISC-V Verification Requirements, Standardization, InfrastructureA lively panel discussion about RISC-V and open-source…Read More Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read MoreDon’t Settle for Less Than Optimal – Get the Perfect Inductor Every Time

The meaning of the word “Veloce” is “blazing fast”. It is the inspiration behind the name of the Ansys VeloceRF electromagnetic (EM) passive device synthesis platform that has been a favorite among RF and high-speed integrated circuit (IC) designers for more than 15 years. VeloceRF is a name that designers automatically connect… Read More

Synopsys is Paving the Way for Success with 112G SerDes and Beyond

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes… Read More

Oops, we did it again! Memory Companies Investment Strategy

We are in the semiconductor market phase where everybody disagrees on what is going on. The market is up; the market is down. Mobile phones are up…. oh no, now they are down. The PC market is up—oh no, we need to wait until we can get an AI PC. The inflation is high—the consumer is not buying.

For us in the industry, the 13-week financial … Read More

An Enduring Growth Challenge for Formal Verification

A high-quality verification campaign including methods able to absolutely prove the correctness of critical design behaviors as a complement to mainstream dynamic verification? At first glance this should be a no-brainer. Formal verification offers that option and formal adoption has been growing steadily, now used in around… Read More

Rigid-flex PCB Design Challenges

From Zion Research I learned that the flexible electronics market was about $13.2B in 2021 and growing at a CAGR of 21%, so that was impressive. There are several factors that make rigid-flex circuit so attractive, like: space efficiency, reduced weight, enhanced reliability, improved signal integrity, streamlined assembly,… Read More

Accelerate SoC Design: DIY, FPGA Boards & Commercial Prototyping Solutions (I)

In the early days, chip designers had to rely on time-consuming simulation results or wait for the engineering sample to validate whether the design meets its intended objectives. With the increasing complexity of SoC designs, the need to accelerate software development has also risen to ensure a timely entry to market.

In the… Read More

The latest ideas on time-sensitive networking for aerospace

Time-sensitive networking for aerospace and defense applications is receiving new attention as a new crop of standards and profiles approaches formal release, anticipated before the end of 2024. CAST, partnering with Fraunhofer IPMS, has developed a suite of configurable IP for time-sensitive networking (TSN) applications,… Read More

Analog Bits Continues to Dominate Mixed Signal IP at the TSMC Technology Symposium

The recent TSMC Technology Symposium in the Bay Area showcased the company’s leadership in areas such as solution platforms, advanced and specialty technologies, 3D enablement and manufacturing excellence. As always, the TSMC ecosystem was an important part of the story as well and that topic is the subject of this post. Analog… Read More

Why NA is Not Relevant to Resolution in EUV Lithography

The latest significant development in EUV lithography technology is the arrival of High-NA systems. Theoretically, by increasing the numerical aperture, or NA, from 0.33 to 0.55, the absolute minimum half-pitch is reduced by 40%, from 10 nm to 6 nm. However, for EUV systems, we need to recognize that the EUV light (consisting … Read More

Build a 100% Python-based Design environment for Large SoC Designs