The introduction of direct die-to-die bonding technology into high volume production has the potential to substantially affect the evolution of the microelectronics industry. The concerns relative to the “end of Moore’s Law”, the diminishing returns of continued (monolithic) CMOS process scaling, and the disruptive effect… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

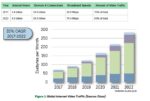

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreSMIC Blacklist puts ASML in Jam

US BIS confirms our prediction of “blacklisting” SMIC

SMIC embargoed from 10NM or better technology

Likely related to ASML pressure & WH scorched earth

Not just the stock

We had received a lot of feedback on our Nov 30th note regarding blacklisting of SMIC suggesting that we were wrong and the only thing blacklisted… Read More

Webinar: Increase Layout Team Productivity with SkillCAD

The Cadence Virtuoso Design System has been one of the premier Integrated Circuit design systems for many years and is used by most major semiconductor companies. While it is powerful and versatile, it is often not optimized for certain complex, repetitive and time-consuming layout design tasks.

The founder and president … Read More

Silicon Catalyst’s Semi Industry Forum – All-Star Cast Didn’t Disappoint

A few weeks ago I wrote about an upcoming event Silicon Catalyst was hosting, the Semiconductor Industry Forum – A View to the Future. I mentioned a high-profile group of presenters: Don Clark, Contributing Journalist, New York Times as moderator; Mark Edelstone, Chairman of Global Semiconductor Investment Banking, Morgan… Read More

Sensor Fusion Brings Earbuds into the Modern Age

Ten years ago, earbuds might have seemed like a mundane product area with little room for exciting developments. Truly Wireless Stereo (TWS) has coincided with an avalanche of innovations that have moved earbuds from a simple transducer for creating sound into being a sophisticated device capable of accepting user commands … Read More

Synopsys is Extending CXL Applications with New IP

Compute Express Link (CXL), a new open interconnect standard, targets intensive workloads for CPUs and purpose-built accelerators where efficient, coherent memory access between a host and device is required. A consortium to enable this new standard is in place, and a lot of heavy hitters are behind the standard, including … Read More

An Accellera Update. COVID Accelerates Progress

Normally I would post this Accellera update during DVCon US but, no surprise, this year is weird. Particularly in conferences going virtual. The last DVCon was in early March of this year, right on the cusp of the shutdown. I was there in person, as was Lu Dai (Chairman of Accellera). Both Synopsys and Cadence had dropped out, citing… Read More

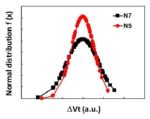

Advanced Process Development is Much More than just Litho

The vast majority of the attention given to the introduction of each new advanced process node focuses on lithographic updates. The common metrics quoted are the transistors per mm**2 or the (high-density) SRAM bit cell area. Alternatively, detailed decomposition analysis may be applied using transmission electron microscopy… Read More

Close the Year with Cliosoft – eBooks, Videos and a Fun Holiday Contest

‘Tis the season, a time when a lot of companies summarize the year, send out holiday greetings and generally wind down until after the New Year. That’s not the case at Cliosoft. Their marketing machine has been in full gear with lots of new, useful and compelling content. I’ll provide a round-up of what’s happening. You can close… Read More

Achronix Talks about FPGAs for Video Processing

The internet keeps adding users and connected devices. According to the numbers in a white paper from Achronix, by 2022 there will be 4.8 billion internet users and 28.5 billion connected devices. Internet traffic will reach 275 exabytes per month. Of this a staggering 83 percent will be video traffic. Moving the data from creators… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center