Every so often a custom silicon socket comes up at a system company that you simply cannot afford to lose if you’re a silicon supplier. These are the types of custom silicon sockets that last for generations of a product, in huge and predictable volumes, and for whatever reason they may become available. It’s not easy to predict… Read More

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More

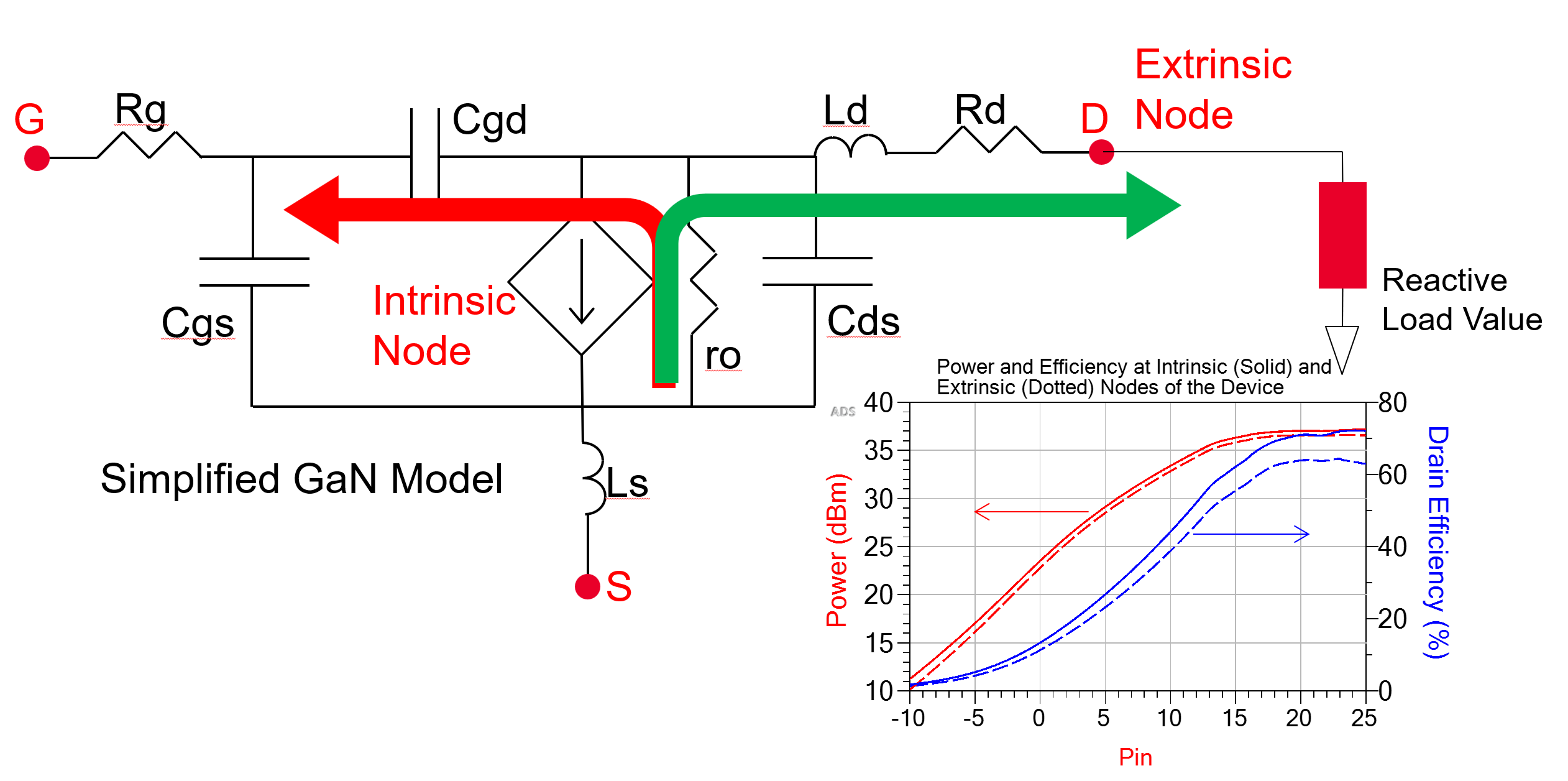

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More WEBINAR: Intrinsic Techniques in RF Power Amplifier DesignLoad-pull power amplifier (PA) design techniques determine the…Read More

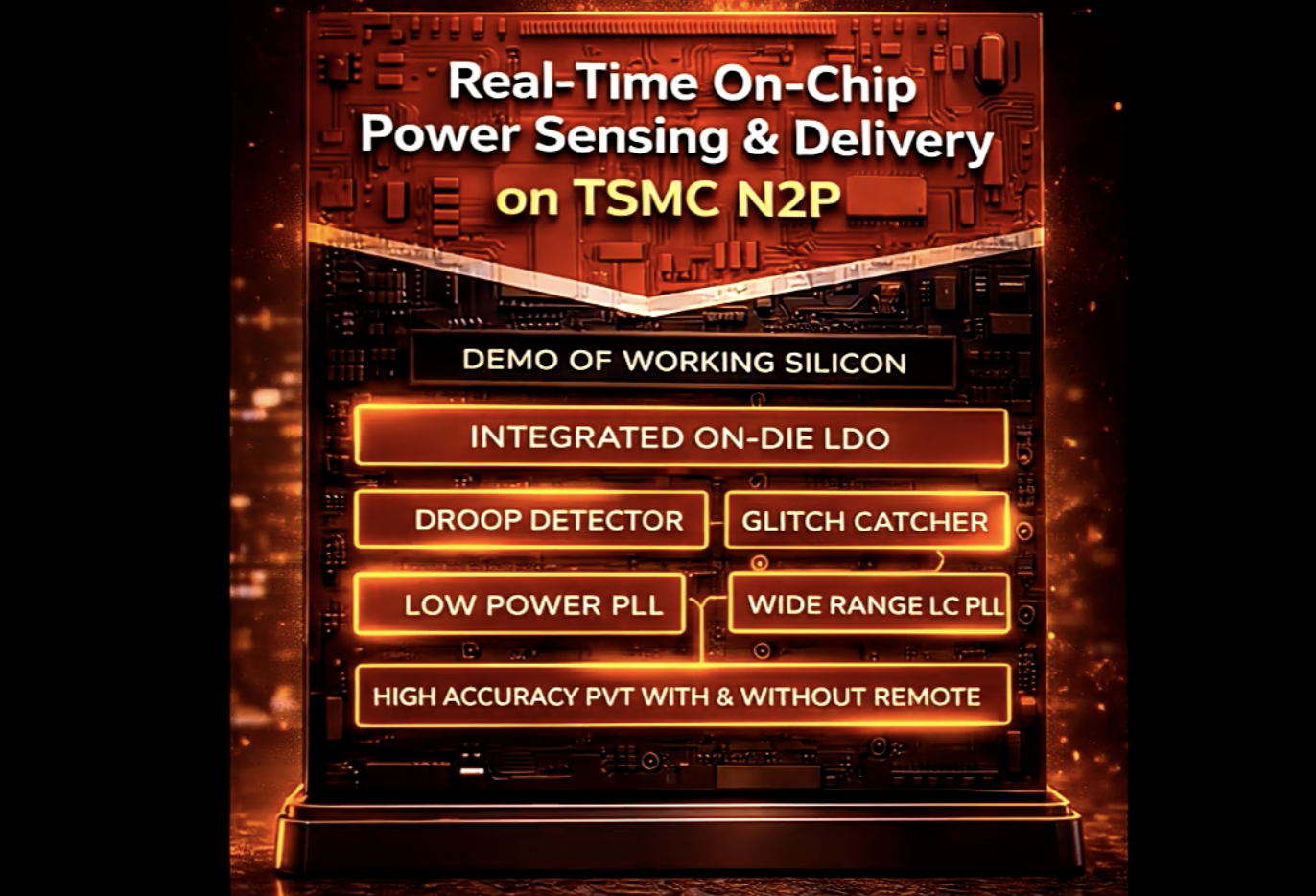

WEBINAR: Intrinsic Techniques in RF Power Amplifier DesignLoad-pull power amplifier (PA) design techniques determine the…Read More Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

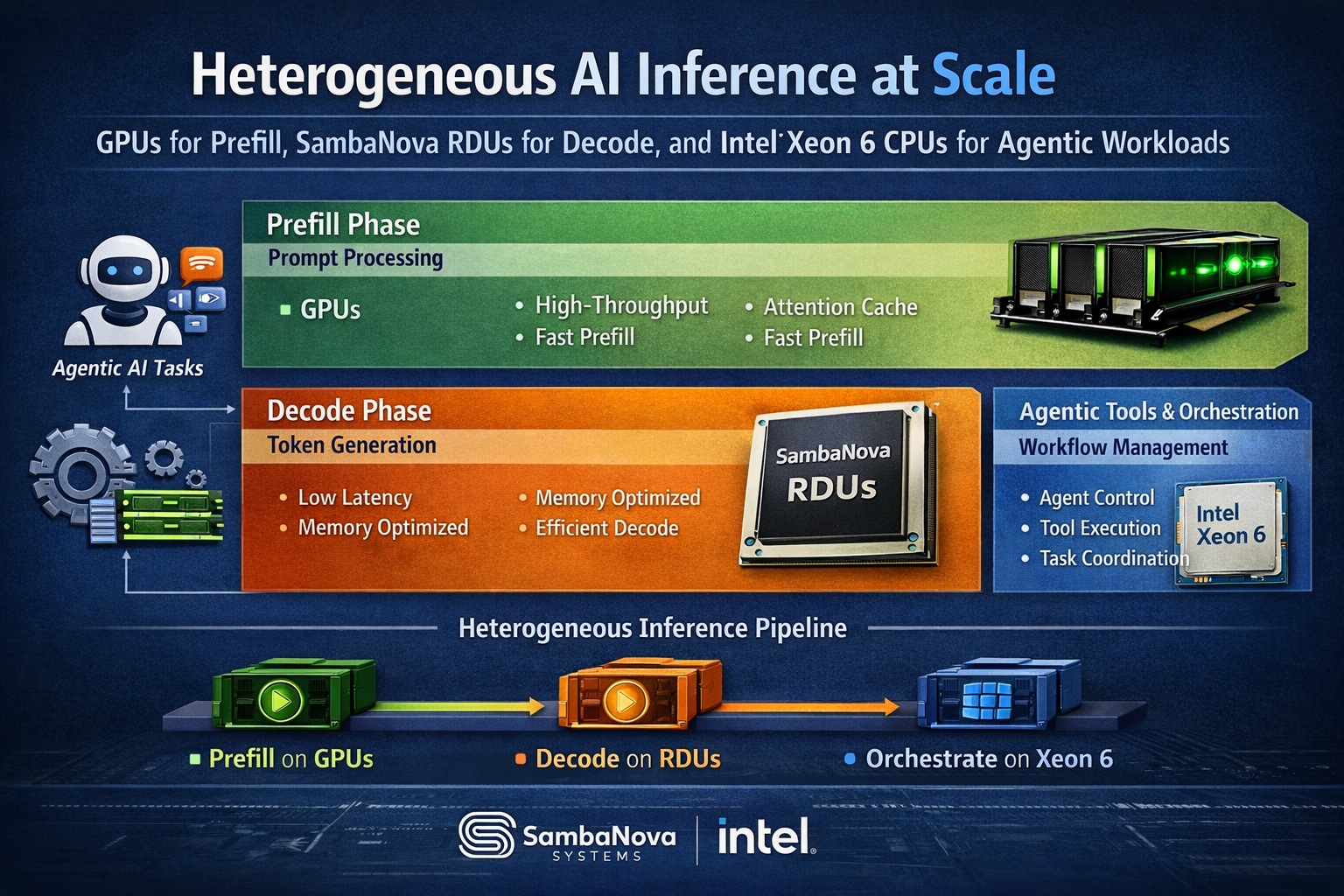

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read MoreAutomotive SoCs Need Reset Domain Crossing Checks

When the number of clock domain crossings (CDCs) in SoCs proliferated it readily became apparent that traditional verification methods were not well suited to ensuring that they were properly handled in the design. This led to the creation of new methods and tools to check for correct interfaces between domains. Now, in automotive… Read More

Siemens EDA is Applying Machine Learning to Back-End Wafer Processing Simulation

There’s a lot to unpack in the title of this post. First, Siemens EDA is the new name for Mentor, a Siemens Business. The organization continues to operate as part of Siemens Digital Industries Software. The organization has released a white paper that describes research done with the American University of Armenia. The work examines… Read More

Uber v Alto Ride Hail Streetfight

Uber, Lyft, Postmates, Instacart and Doordash were successful in their nearly $200M effort to pass California’s Proposition 22 in November – to allow gig operators to avoid treating their drivers as full-time employees with all of the associated employee benefits and legal protections. In the midst of a devastating pandemic… Read More

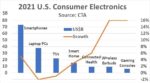

CES 2021 Goes All Digital

CES, the massive consumer technology show put on by the Consumer Technology Association (CTA), was held this week. Due to the global COVID-19 pandemic, CES 2021 was all digital. Last year, CES 2020 had over 170,000 attendees from over 160 countries and 4,400 exhibiting companies.

CES 2020 was held January 7-10, 2020 in Las Vegas,… Read More

CES 2021 and all things Cycling Technology

It’s January so time to give you another summary of what I’ve found at CES 2021 about new cycling products that have electronic content. During the pandemic in 2020 we’ve seen a surge in sales for bicycles, e-bikes, spin bikes and trainers as people wanted a simple way of getting around town running errands, or… Read More

Podcast EP3: Tomorrow’s Semiconductors with Jim Hogan

Dan and Mike are joined by industry luminary Jim Hogan. In a rare interview, Jim talks about his life – how he got into semiconductors, EDA and venture investing. Jim’s time at Cadence as well as his work at ARM are explored. Jim also provides a concise and informative overview of how venture investing works. The podcast… Read More

CEO Interview: Arun Iyengar of Untether AI

I had a chance to catch up with Arun Iyengar, CEO of Untether AI. Untether AI recently unveiled its tsunAImi accelerator cards powered by the company’s runAI devices. Using at-memory computation, Untether AI breaks through the barriers of traditional von Neumann architectures, offering industry-leading compute density … Read More

ISS 2021 – Scotten W. Jones – Logic Leadership in the PPAC era

I was asked to give a talk at the 2021 ISS conference and the following is a write up of the talk.

The title of the talk is “Logic Leadership in the PPAC era”.

The talk is broken up into three main sections:

- Background information explaining PPAC and Standard Cells.

- A node-by-node comparisons of companies running leading edge logic

HFSS – A History of Electromagnetic Simulation Innovation

In the 155 years since James Clerk Maxwell introduced the world to Maxwell’s Equations in the “Dynamic Theory of the Electromagnetic Field” there have been some amazing breakthroughs and avenues of insight. As a young electrical engineering student, we are introduced to the set of equations describing electromagnetic waves,… Read More

Is Intel About to Take Flight?