The other day, I was having one of my regular chats with Cristian Amitroaie, CEO and co-founder of AMIQ EDA. One of our subjects was a topic that we discussed last year, the wide range of languages and formats that chip design and verification engineers use these days. AMIQ EDA has put a lot of effort into adding support for many of these… Read More

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

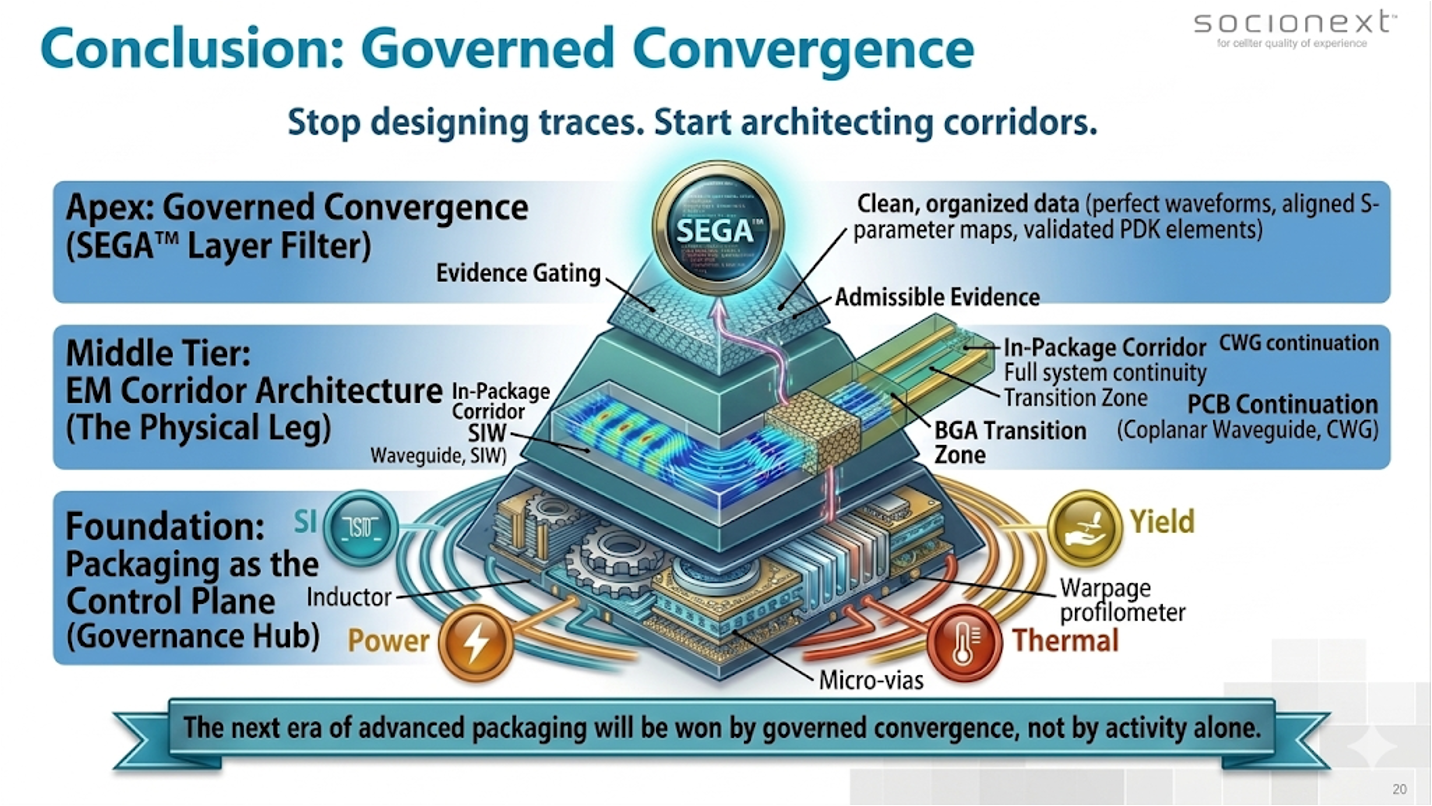

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreMRAM Magnetic Immunity – Empirical Study Summary

The main threat for the wide adoption of MRAM memories continues to be their lack of immunity to magnetic fields. MRAM magnetic immunity (MI) levels has seen significant research over the years and new data is continuously published from the main MRAM vendors.

This data, however, is rarely compared to magnetic field exposure scenarios… Read More

Can Our Privacy be Protected in Cars?

“Those who would give up essential liberty to purchase a little temporary safety deserve neither liberty nor safety.” — Benjamin Franklin

I hope Ben Franklin was not opposed to enhancing driving safety, but he may have looked with a jaundiced eye at the proliferation of in-cabin driver monitoring technology. … Read More

SALELE Double Patterning for 7nm and 5nm Nodes

In this article, we will explore the use of self-aligned litho-etch-litho-etch (SALELE) double patterning for BEOL metal layers in the 7nm node (40 nm minimum metal pitch [1]) with DUV, and 5nm node (28 nm minimum metal pitch [2]) with EUV. First, we mention the evidence that this technique is being used; Xilinx [3] disclosed the… Read More

Podcast EP13: The Three Pillars of Verification with Adnan Hamid

Dan goes on a scenic tour of verification with Adnan Hamid, founder and CEO of Breker Verification Systems. We discuss the rather unusual way Adnan got into semiconductors and SoC verification. Adnan then breaks down the verification task into its fundamental parts to reveal what the three pillars of verification are and why … Read More

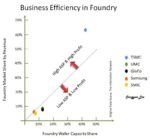

Foundry Fantasy- Deja Vu or IDM 2?

– Intel announced 2 new fabs & New Foundry Services

– Not only do they want to catch TSMC they want to beat them

– It’s a very, very tall order for a company that hasn’t executed

– It will require more than a makeover to get to IDM 2.0

Intel not only wants to catch TSMC but beat them at their own … Read More

Intel Takes Another Shot at the Enticing Foundry Market

Intel made a big splash on March 23, 2021 by doubling down on manufacturing with the creation of Intel Foundry Services (IFS). The big announcement was supported by potential customers such as Qualcomm, Cisco, Ericsson, Google, Amazon, Microsoft, and IBM. With an accompanying $20B investment, the EDA and equipment industries,… Read More

Flex Logix Closes $55M in Series D Financing and Accelerates AI Inference and eFPGA Adoption

Flex Logix is a unique company. It is one of the few that supplies both FPGA and embedded FPGA technology based on a proprietary programmable interconnect that uses half the transistors and half the metal layers of traditional FPGA interconnect. Their architecture provides some rather significant advantages. I wrote about their… Read More

Reducing Compile Time in Emulation. Innovation in Verification

Is there a way to reduce cycle time in mapping large SoCs to an FPGA-based emulator? Paul Cunningham (GM, Verification at Cadence), Jim Hogan (RIP) and I continue our series on research ideas. As always, feedback welcome.

The Innovation

This month’s pick is Improving FPGA-Based Logic Emulation Systems through Machine Learning… Read More

Smarter Product Lifecycle Management for Semiconductors

Product Lifecycle Management (PLM) for electronic systems has moved from a passive ‘fire and forget’ approach to one that is intimately involved not only during design, but also throughout the entire life of every unit delivered to the field. Siemens EDA has a white paper titled “Tessent Silicon Lifecycle Solutions” that talks… Read More

Solving the EDA tool fragmentation crisis