-$80B + in WFE with strong back half in 2021

-Trailing edge strength adds to overall great demand

-Supply side headwinds require effort- Malaysia now open

-It just comes down to execution which Lam has done well

Nice beat and sandbagged guide

As Lam has done consistently for many quarters now, they beat numbers with Revenues of $4.15B… Read More

Dan is joined by Dr. Rosemary Francis. Rosemary was the managing director and CEO of Ellexus Ltd. before its acquisition by Altair. Dan explores the I/O profiling technology Ellexus brought to Altair, it’s impact and the implications for the future. A behind-the-scenes view of the acquisition is also provided.

Dr. Rosemary… Read More

Introduction

Intel recently provided a detailed silicon process and advanced packaging technology roadmap presentation, entitled “Intel Accelerated”. The roadmap timeline extended out to 2024, with discussions of Intel client, data center, and GPU product releases, and especially, the underlying technologies to be … Read More

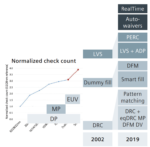

Electronic design automation (EDA) has come a long way from its beginnings. It has enabled chip engineers from specifying designs directly in layout format during the early days to today’s capture in RTL format. Every advance in EDA has made the task of designing a chip easier and increased the design team productivity, enabling… Read More

As I read both the popular and technical press each week I often see articles about computer systems being hacked, and here’s just a few vulnerabilities from this week:

…

Read More

In every chip, power is a progressive problem to be solved. Designers have long had to rely on a combination of experience and knowledge to tackle this dilemma, typically having to wait until after silicon availability to perform power analysis with realistic software workloads. However, this is too late in the game, as it becomes… Read More

Instrumenting post-silicon validation is not a new idea but here’s a twist. Using (pre-silicon) emulation to choose debug observation structures to instrument in-silicon. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research… Read More

A decade ago, many of us heard commentaries on how entrepreneurs were turned down by venture capitalists for not including a cloud strategy in their business plan, no matter what the core business was. Humorous punchlines such as, “It’s cloudy without any clouds” and “Add some cloud to your strategy and your future will be bright… Read More

Intel presented yesterday on their plans for process technology and packaging over the next several years. This was the most detailed roadmap Intel has ever laid out. In this write up I will analyze Intel’s process announcement and how they match up with their competitors.

10nm Super Fin (SF)

10nm is now in volume production in three… Read More

Ansys Multiphysics Platformby Tom Dillinger on 07-26-2021 at 10:00 amCategories: Ansys, Inc., EDA

Background

Traditionally, the interface between chip designers and system power, packaging, reliability, and mechanical engineering teams was a relatively straightforward exchange of specifications. Chip designers developed preliminary power dissipation estimates, often based on a simplifying power/mm**2 value. … Read More

Is Intel About to Take Flight?