In every chip, power is a progressive problem to be solved. Designers have long had to rely on a combination of experience and knowledge to tackle this dilemma, typically having to wait until after silicon availability to perform power analysis with realistic software workloads. However, this is too late in the game, as it becomes a costly and time-consuming proposition to resolve power issues post-silicon. In this blog post, I’ll explain how you can achieve actionable power verification results in hours on billion-gate designs early on. With this capability, you can find the critical regions and time windows for peak power and, thus, optimize your RTL and software.

Performing power analysis post-silicon introduces the risk of missing critical high-power situations, which can create significant cost and product adoption problems. The downsides of being wrong about power? A customer could opt to go with another chip vendor if a design misses the promised power target. Or, a system designer might be forced to dial back chip performance to maintain the targeted power envelope—an unfavorable tradeoff in applications that rely on fast compute performance. In this post, which was originally published on the “From Silicon to Software” blog, we’ll take a closer look at some SoC application areas where accurate power analysis is essential.

GPUs

Traditional GPU applications are known entities by comparison, but this doesn’t make the power analysis task any easier. Consider a GPU designed for a laptop computer. You can run power analysis at certain measurement points over a period of time. However, with potentially up to 10 million clock cycles, this approach is clearly not exhaustive—which is why designers traditionally have had to rely on their best estimates for power.

Artificial Intelligence

In artificial intelligence (AI) chips, the applications as well as the software stack for AI applications and architectures are all new territory, which poses more challenges from a power profiling perspective. Yet, the potential rewards of optimizing AI applications for power are great. Power efficiency, after all, is an advantage that AI chip designers would love to be able to tout, along with fast compute performance.

5G

Another power-critical application is 5G, which is all about high performance and low latency. 5G applications involve a lot of parallel processing and high frequencies, but, with only so much power available, they must be optimized to run efficiently. This is particularly true for radio head chips.

Data Centers

Data centers, especially hyperscale data centers, are built on lightning-fast, energy-efficient chips that can help maximize total system throughput. With billions of gates along with complex software workloads, data center SoCs come with particularly demanding verification and software bring-up requirements.

Mobile

Given their compact form factor and desired long battery life, mobile devices such as smartphones cannot afford to use chips that consume too much power. While their workloads have grown in complexity, these devices—even the power-hungry GPUs—must still be able to accommodate these workloads power efficiently.

How a Fast Power Emulator Solves the Power Profiling Challenge

As meeting dynamic power requirements becomes increasingly difficult, chip designers often consider power to be their top verification challenge. Dynamic power verification requires finding peak power. Yet, critical peak power events are driven by actual software workloads. Simulation can identify peak power that falls above as well as below the power budget, but in billion-gate designs, it will only be able to catch the real critical events by pure luck, as the windows a simulation based approach can consider are much too small. A signoff tool would provide accurate power measurements, but if it is used on the wrong time window, the designer would not be able to determine which window has the highest power.

Identifying low-power bugs requires running software workloads. Small tests won’t expose realistic workload-driven power bugs. What’s needed is:

- Real firmware and operating system at pre-silicon testing

- Emulation to verify power over millions or billions of cycles

- Pre-silicon power verification for debug, which isn’t possible with actual silicon

High-speed emulation allows design teams to perform power verification earlier in the design cycle, so they can minimize the risks of power bugs and missed SoC power goals. Indeed, a fast power emulator can be the answer to the hardware/software power verification dilemma, providing better accuracy across a broader window. The ideal emulator would be able to run multiple iterations a day on large designs with realistic workloads. By doing so, chip designers can gain actionable insights into the power profile of their designs.

Actionable Insights in Hours

With multi-billion-gate SoC workloads in mind, Synopsys has unveiled its new Synopsys ZeBu® Empower emulation system for hardware/software power verification. Delivering maximum compute performance, ZeBu Empower can perform multiple iterations a day, providing actionable results in hours. Based on the resulting power profiles, hardware and software designers can, early on, identify areas where they can improve dynamic and leakage power. ZeBu Empower utilizes ZeBu Server fast emulation hardware technology to provide the short turnaround times.

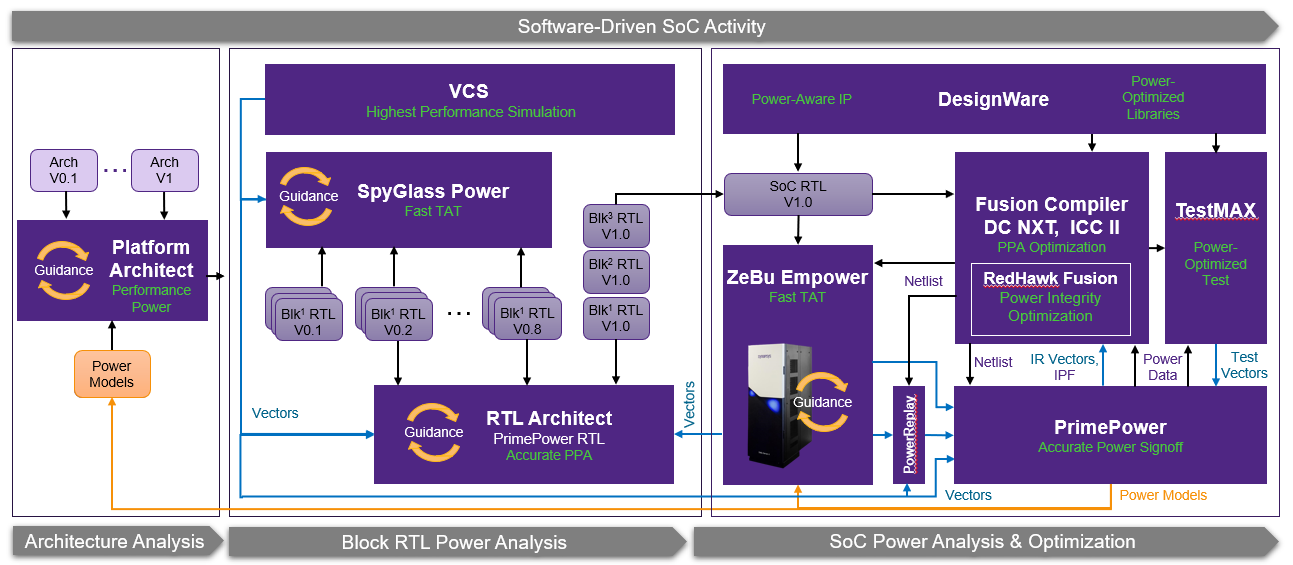

ZeBu Empower also feeds forward power-critical blocks and time windows into the Synopsys PrimePower engine to accelerate RTL power analysis and gate-level power signoff. Both ZeBu Empower and PrimePower are part of the Synopsys software-driven low-power solution. Pictured in the diagram below, the low-power solution provides an end-to-end flow and methodology spanning from architecture analysis to block RTL power analysis to SoC power analysis and optimization.

The Synopsys software-driven low-power solution is designed to help reduce overall dynamic and static power consumption of ICs.

Summary

Power might just be the most challenging part of the power, performance, and area (PPA) equation. And when it comes to multi-billion-gate designs, the complexity in achieving accurate power profiles only grows. However, with the fast power emulation solution from Synopsys, designs teams can now find the critical regions and time windows for peak power, so they can optimize their RTL and their software. By taking advantage of the comprehensive Synopsys low-power flow, designers gain tools that can help them meet their PPA targets. Given the heavy workloads and performance demands of applications like GPUs, AI, 5G, data centers, and mobile, any solution that can provide a more accurate power picture should be a welcome addition to any designer’s PPA toolkit.

Also Read:

Driving PPA Optimization Across the Cubic Space of 3D IC Silicon Stacks

Die-to-Die Connections Crucial for SOCs built with Chiplets

Mars Perseverance Rover Features First Zoom Lens in Deep Space

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.