Yes, it is that time of year again, the 2026 TSMC Technology Symposium kick-off event in Silicon Valley. TSMC has never been in a better position to forecast the future of semiconductor technology and the industry itself. TSMC closely collaborates with the top semiconductor companies around the world and the top players in the … Read More

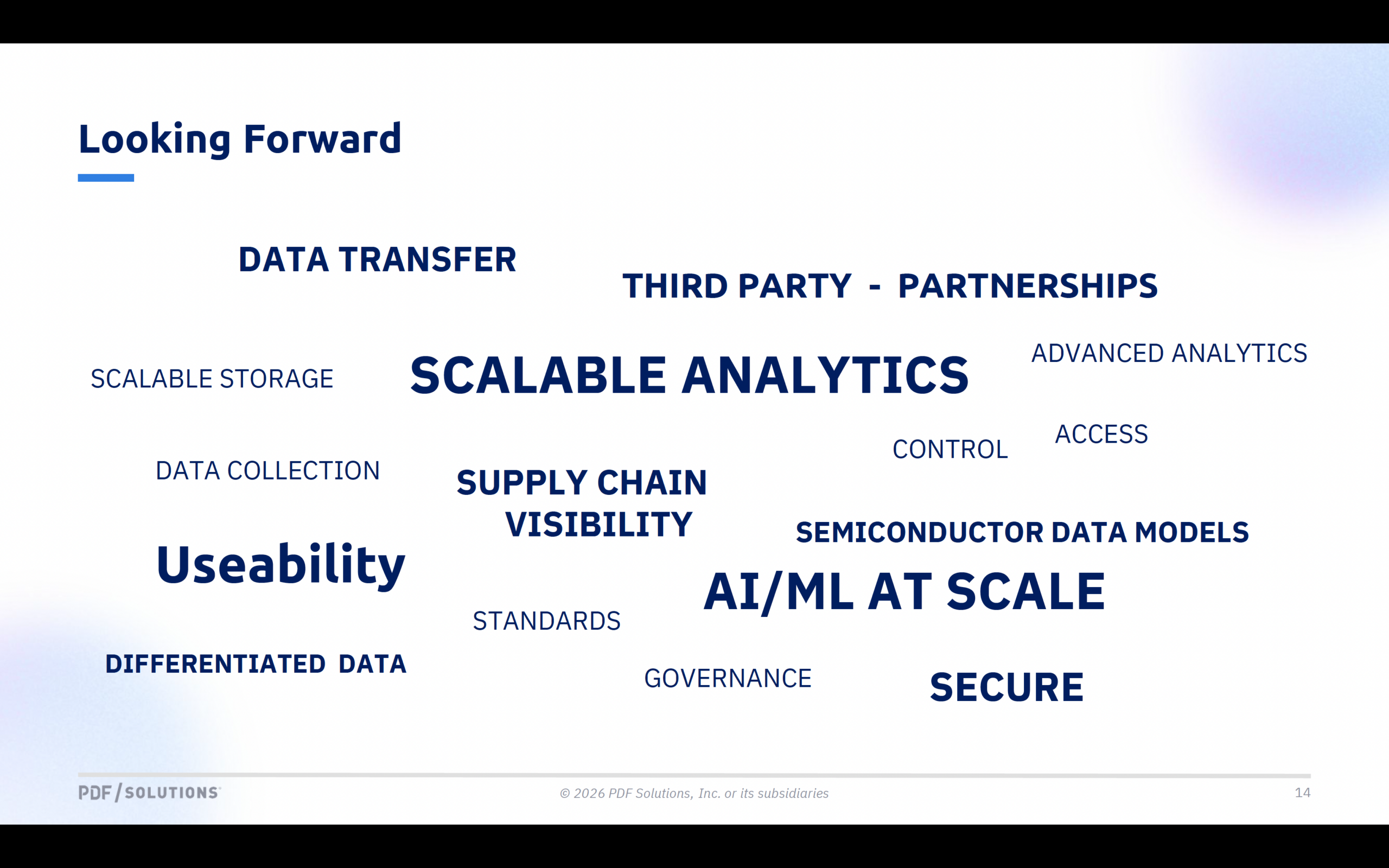

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read MoreCould Neutral Atoms Take the Lead in Quantum Computing?

As of my recent posts on quantum computing (QC), superconducting QC is the leading technology contender, exemplified in systems from IBM, Google, and Fujitsu. Other technologies such as ion trap, neutral atom, photonic and quantum dot have generally been viewed as intriguing but second tier. I just read a very recent paper suggesting… Read More

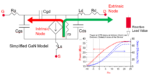

Transitioning Voltage Regulator Design From Unidirectional To Bidirectional

An interesting article by Nazzareno Rossetti, published in How2Power Today, explores the transition from designing traditional unidirectional voltage regulators to bidirectional converters essential for modern energy management systems (EMSs). These systems optimize energy flow and storage among electric vehicles,… Read More

How to Overcome the Advanced Node Physical Verification Bottleneck

It is well-known that advanced semiconductor process technology presents substantial challenges across the full design flow and global supply chain. In this piece, we will focus on a particularly difficult problem – physical verification. This design step is the final gate to manufacturing. Producing a final tape‑out GDS … Read More

Is Intel About to Take Flight?

The Pan Am–Boeing playbook and what Musk’s Terafab order could mean for Intel Foundry

“We either build the Terafab or we don’t have the chips.” That’s Elon Musk, speaking to Reuters, stating a supply constraint as plainly as anyone has stated one. TSMC is sold out. Samsung is committed. The existing supply chain can’t expand fast… Read More

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of Chiplets

The recent Chiplet Summit 2026 was a great place to learn about new chiplet designs, emerging standards, and a growing array of support technologies to help design and manufacture chiplet-based systems. In my travels at the show, I found a lot of technology that fit these descriptions. But there were also companies at the show that… Read More

WEBINAR: Intrinsic Techniques in RF Power Amplifier Design

Load-pull power amplifier (PA) design techniques determine the optimal impedances at the power transistor’s extrinsic reference plane, which is the physically accessible boundary for measurement or simulation. This reference plane can be the package transistor leads, die bond pads, or IC chip terminals. It includes… Read More

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology Symposium

Analog Bits has a way of stealing the show at every event they attend. The formula is actually quite straight-forward – come to the show with the most relevant, highest impact IP running on the most advanced process. The company will be applying this strategy again at the upcoming TSMC 2026 Technology Symposium with an array of real-time… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint

SambaNova Systems and Intel have introduced a blueprint for heterogeneous inference that reflects a significant shift in how modern large language model (LLM) workloads are deployed. Instead of relying on a single accelerator type, the proposed architecture assigns different phases of inference to specialized hardware:… Read More

CEO Interview with Johan Wadenholt Vrethem of Voxo

With over two decades of experience bridging technology and business, Johan Wadenholt Vrethem focused on harnessing AI to transform how organizations operate and engage with their customers. After leading critical digital initiatives and client engagements in the banking and finance sectors at CGI, Johan co-founded Voxo… Read More

Is Intel About to Take Flight?