The big fake news last week came from a report out of China stating that TSMC won a big Intel order for 3nm wafers. We have been talking about this for some time on SemiWiki so this is nothing new. Unfortunately, the article mentioned wafer and delivery date estimates that are unconfirmed and from what I know, completely out of line. … Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

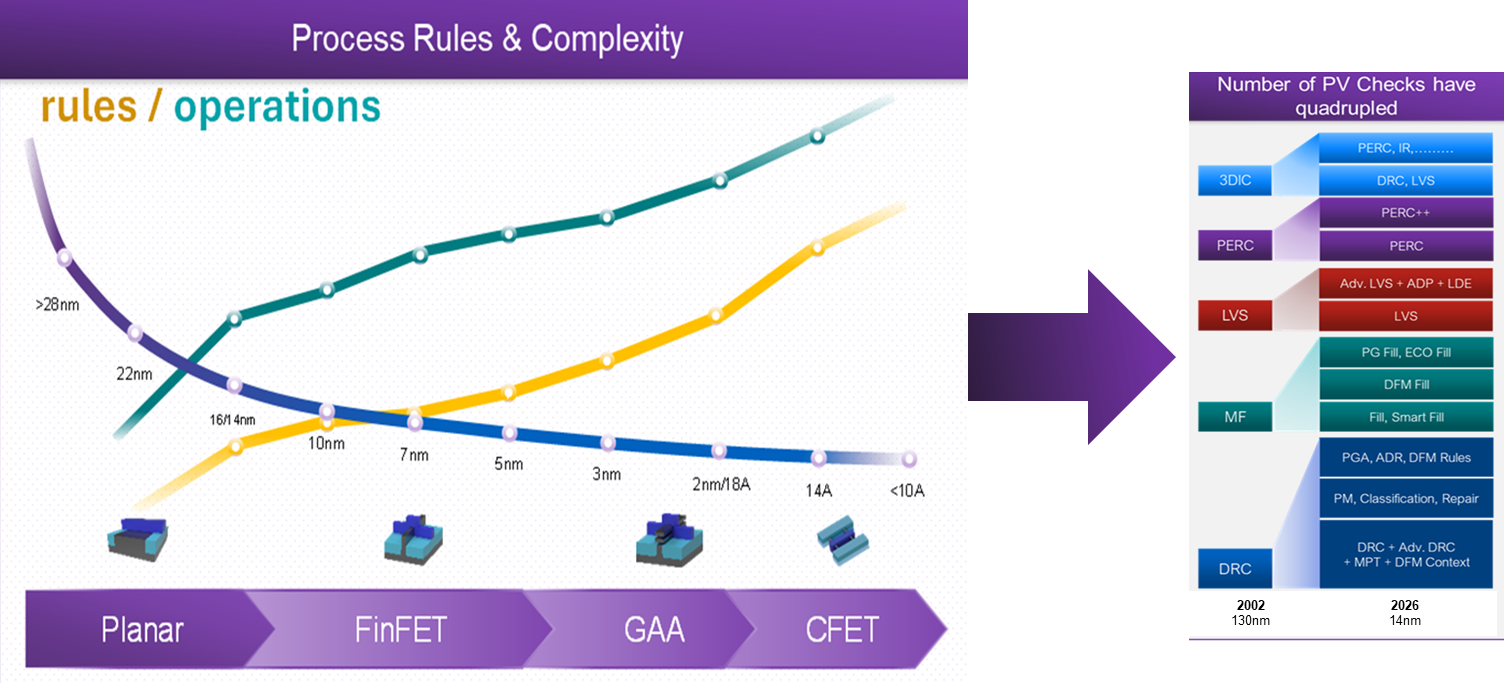

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read MoreControlling the Automotive Network – CAN and TSN Update

Cars are hotbeds of systems innovation. I’ve been fortunate to be asked to write about many of these areas, from the MEMS underlying sensors to ISPs and radars, intelligent imaging and sensor fusion. And many aspects of design for safety within the SoCs around a car. But I haven’t written much about the networks connecting these … Read More

Flex Logix and Socionext are Revolutionizing 5G Platform Design

The world is buzzing with 5G deployment news. It seems the entire planet anxiously awaits the step function improvement in bandwidth and latency promised by this new technology. When there is additional deployment, it’s news. When there are new chipsets and devices supporting the standard it’s news. But when there is a fundamental… Read More

How Hyperscalers Are Changing the Ethernet Landscape

It’s all about bandwidth these days – fueling hyperscale data centers that support high-performance and cloud computing applications. It’s what enables you to stream a movie on your smart TV while your roommate plays an online game with friends located in different parts of the country. It’s what makes big data analytics run swiftly… Read More

You Get What You Measure – How to Design Impossible SoCs with Perforce

We all know that a trusted, reliable, and well-integrated design flow is critical to successful advanced SoC design. So is proven, robust IP. While these elements are necessary for success, they are not, by themselves, sufficient. There are other aspects to consider – measurement, tracking and coordination. We’ve all heard … Read More

S2C FPGA Prototyping solutions help accelerate 3D visual AI chip

3D vision technology is rapidly evolving. Compared to 2D vision technology that deals with planar information, 3D vision works with physical information, including depth, which makes it possible to recognize and measure objects with curved surfaces and arcs. In addition, as deep machine learning and big data computing technologies… Read More

Your Car Should be Smarter

SEC. 24102. HIGHWAY SAFETY PROGRAMS.

Section 402 of title 23, United States Code, is amended — by striking ‘‘accidents’’ each place it appears and inserting ‘‘crashes’’; by striking ‘‘accident’’ each place it appears and inserting ‘‘crash’’ — from amendment to Senate infrastructure legislation

The Biden Administration

Samtec Dominates DesignCon 2021

DesignCon has grown over the years to become a true system design show. The show’s tagline is WHERE THE CHIP MEETS TO BOARD. This is just the beginning. Besides the chip and the board there are all the challenges, opportunities, and options to get signals reliably propagated throughout the entire system. Power, signal integrity,… Read More

Podcast EP33: Processing AI Workloads

Dan and Mike are joined by Dana McCarty, vice president of sales and marketing at Flex Logix Technologies, Inc. Using an eFPGA-based architecture for processing AI workloads is discussed, along with typical applications and power, performance and cost benefits. The competitive positioning of Flex Logix’s InferX X1 … Read More

TSMC Explains the Fourth Era of Semiconductor – It’s All About Collaboration

The 32nd VLSI Design/CAD Symposium just occurred in a virtual setting. The theme of the event this year was “ICs Powering Smart Life Innovation”. There were many excellent presentations across analog & RF, EDA & testing, digital & system, and emerging technology. There were also some excellent keynotes, and this… Read More

Is Intel About to Take Flight?