Dynamic event-based simulation of RTL models has traditionally been the workhorse verification methodology. A team of verification engineers interprets the architectural specification to write testbenches for various elements of the design hierarchy. Test environments at lower levels are typically exercised then … Read More

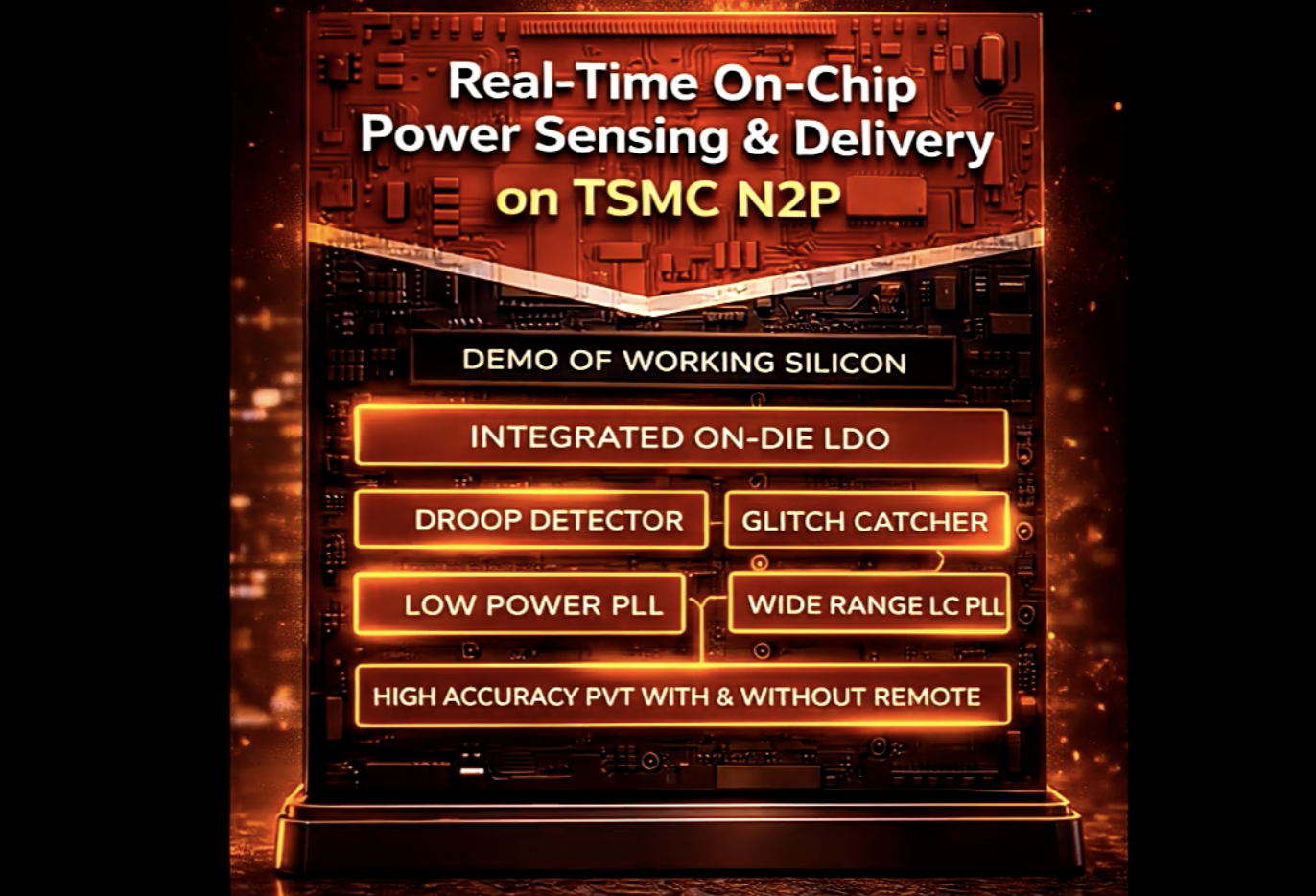

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

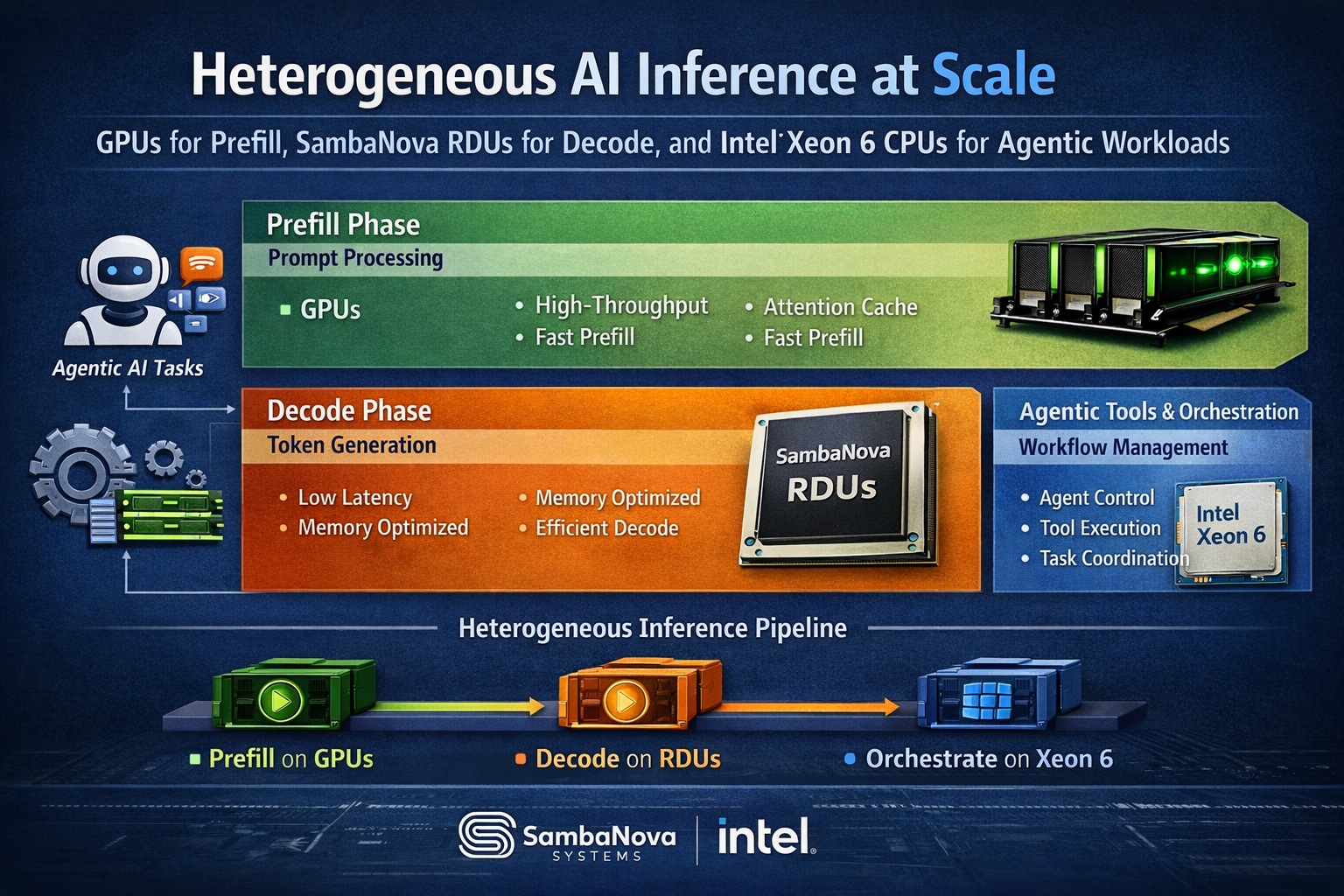

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

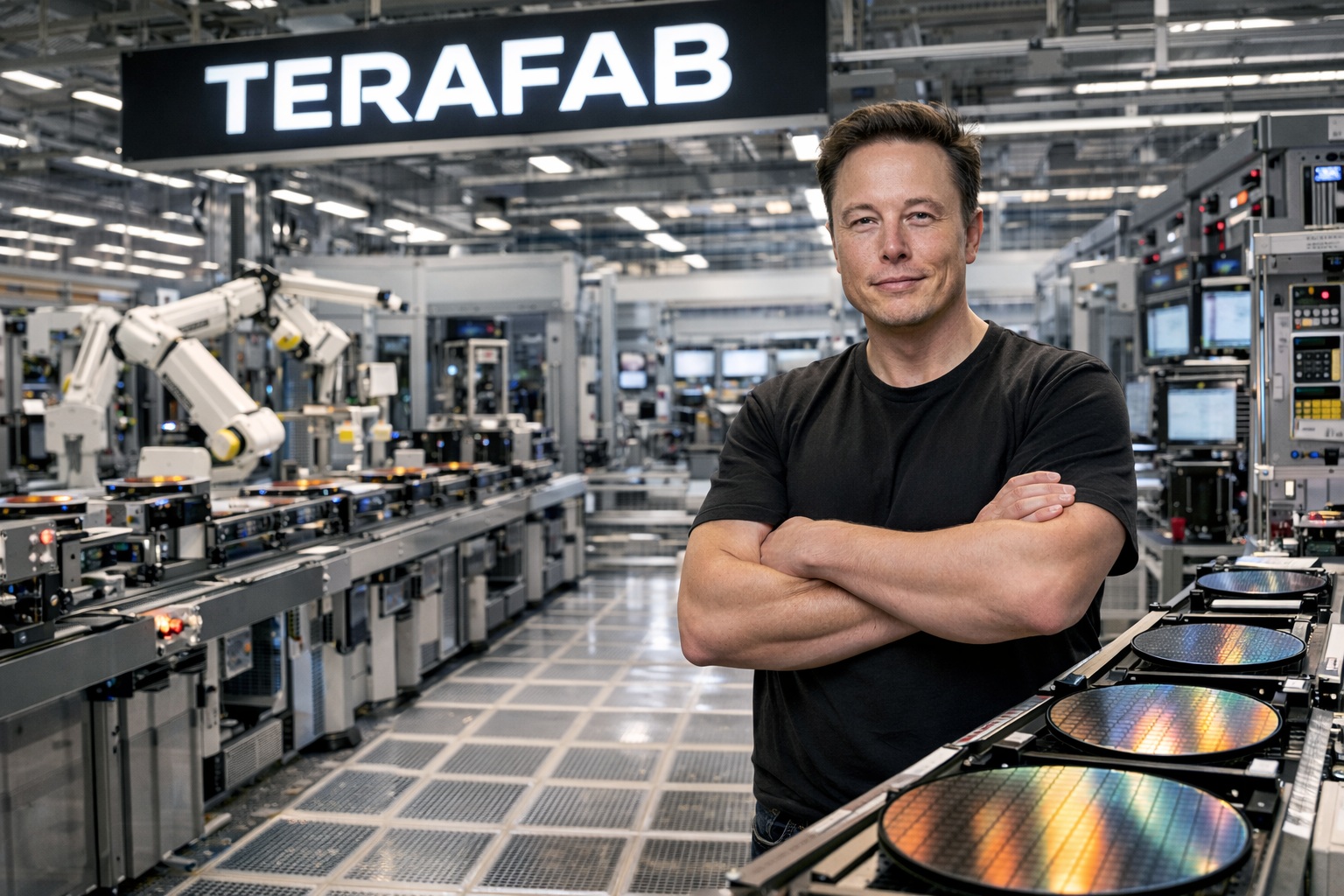

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreTSMC’s Reliability Ecosystem

TSMC has established a leadership position among silicon foundries, based on three foundational principles:

- breadth of technology support

- innovation in technology development

- collaboration with customers

Frequent SemiWiki readers have seen how these concepts have been applied to the fabrication and packaging technology… Read More

Synopsys Tutorial on Dependable System Design

Synopsys hosted a tutorial on the last day of DVCon USA 2022 on design/system dependability. Which here they interpret as security, functional safety, and reliability analysis. The tutorial included talks from DARPA, AMD, Arm Research and Synopsys. DARPA and AMD talked about general directions and needs, Arm talked about their… Read More

The Importance of Low Power for NAND Flash Storage

Even though we all know that reducing power consumption in NAND Flash Storage is a good idea, it is worthwhile to take a deeper dive into the underlying reasons for this. A white paper by Hyperstone, a leading developer of Flash controllers, discusses these topics providing useful insight into the problem and its solutions. The … Read More

Security Requirements for IoT Devices

Designing for secure computation and communication has become a crucial requirement across all electronic products. It is necessary to identify potential attack surfaces and integrate design features to thwart attempts to obtain critical data and/or to access key intellectual property. Critical data spans a wide variety… Read More

Designing a FinFET Test Chip for Radiation Threats

Much of the technology that goes into aerospace applications is some of the most advanced technology that exists. However, these same systems must also offer the highest level of reliability in what is arguably an extremely difficult environment. For semiconductors a major environmental risk in aerospace applications are … Read More

Bridging Analog and Digital worlds at high speed with the JESD204 serial interface

We are delighted to showcase our “Bridging Analog and Digital worlds at high speed with the JESD204 Serial Interface” webinar on April 20th, in case you missed the live webinar back in February 2022.

To meet the increased demand for converter speed and resolution, JEDEC proposed the JESD204 standard describing a new efficient … Read More

EUV Resist Absorption Impact on Stochastic Defects

Stochastic defects continue to draw attention in the area of EUV lithography. It is now widely recognized that stochastic issues not only come from photon shot noise due to low (absorbed) EUV photon density, but also the resist material and process factors [1-4].

It stands to reason that resist absorption of EUV light, which is … Read More

A Blanche DuBois Approach Won’t Resolve Traffic Trouble

Near the end of Tennessee Williams’ “A Streetcar Named Desire” the Blanche DuBois character, who has suffered a mental breakdown following an implied rape, tells the doctor and matron who have come to take her to the hospital: “Whoever you are – I have always depended on the kindness of strangers.” Sadly, this is the… Read More

Cadence and DesignCon – Workflows and SI/PI Analysis

DesignCon 2022 is back to a live conference, from Tuesday, April 5th through Thursday, April 7th, at the Santa Clara Convention Center.

Introduction

DesignCon is a unique gathering in our industry. Its roots incorporated a focus on complex design and analysis requirements of (long-reach) high-speed interfaces. Technical… Read More

Is Intel About to Take Flight?