It has been an exciting time in the semiconductor industry and the excitement is far from over. Years 2022 and 2023 will be more challenging in many different ways and live activities have just begun. The cornerstones to the semiconductor industry are the foundries so I look forward to the live foundry events coming up in October,… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreThree Ways to Meet Manufacturing Rules in Advanced Package Designs

Often designers are amazed at the diversity of requirements fabricators and manufacturers have for metal filled areas in advanced package designs. Package fabricators and manufacturers do not like solid metal planes or large metal areas. Their strict metal fill requirements address two main issues. The dielectric and metal… Read More

Synopsys Vision Processor Inside SiMa.ai Edge ML Platform

SiMa.ai just announced that they achieved first silicon success on their new MLSoC, for AI applications at the edge, using Synopsys’ design, verification, IP and design services solutions. Notably this design includes the Synopsys ARC® EV74 processor (among other IP) for vision processing. SiMa.ai claim their platform, now… Read More

Podcast EP106: SoC Verification Flows and Methodologies with Sivakumar P R of Maven Silicon

Dan is joined by Sivakumar P R, the Founder and CEO of Maven Silicon. He is responsible for the company’s vision, overall strategy, business, and technology. He is also the Founder and CEO of ASIC Design Technologies.

Dan and Sivakumar discuss SoC Verification Flows and Methodologies based on his article published on SemiWiki.… Read More

Machine Learning in the Fab at #59DAC

It used to be true that a foundry or fab would create a set of DRC files, provide them to designers, and then the process yield would be acceptable, however if the foundry knows more details about the physical implementation of IC designs then they can improve the yield. Using a digital twin of the design, process and metrology steps… Read More

Ultra-efficient heterogeneous SoCs for Level 5 self-driving

The latest advanced driver-assistance systems (ADAS) like Mercedes’ Drive Pilot and Tesla’s FSD perform SAE Level 3 self-driving, with the driver ready to take back control if the vehicle calls for it. Reaching Level 5 – full, unconditional autonomy – means facing a new class of challenges unsolvable with existing technology… Read More

WEBINAR: Scalable, On-Demand (by the Minute) Verification to Reach Coverage Closure

Verification has long been the most time-consuming and often resource-intensive part of chip development. Building out the infrastructure to tackle verification can be a costly endeavor, however. Emerging and even well-established semiconductor companies must weigh the Cost-of-Results (COR) against Time-to-Results

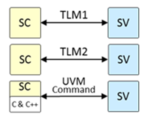

Connecting SystemC to SystemVerilog

Siemens EDA is clearly on a mission to help verifiers get more out of their tools and methodologies. Recently they published a white paper on UVM polymorphism. Now they have followed with a paper on using UVM Connect, re-introducing how to connect between SystemC and SystemVerilog. I’m often mystified by seemingly overlapping… Read More

Truechip: Customer Shipment of CXL3 VIP and CXL Switch Model

The tremendous amount of data generated by AI/ML driven applications and other hyperscale computing applications have forced the age old server architecture to change. The new architecture is driven by the resource disaggregation paradigm, wherein memory and storage are decoupled from the host CPU and managed independently… Read More

WEBINAR: Unlock your Chips’ Full Data Transfer Potential with Interlaken

Way back in the early 2000s when XAUI was falling short on link flexibility a search for an alternative chip-to-chip data transfer interface with SPI like features lead Cisco Systems and Cortina System to put forward the proposal for the Interlaken standard. The new standard married the best of XAUI’s serialized data and SPI’s … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center