The Pan Am–Boeing playbook and what Musk’s Terafab order could mean for Intel Foundry

“We either build the Terafab or we don’t have the chips.” That’s Elon Musk, speaking to Reuters, stating a supply constraint as plainly as anyone has stated one. TSMC is sold out. Samsung is committed. The existing supply chain can’t expand fast… Read More

The rapid acceleration of artificial intelligence (AI) workloads is placing unprecedented demands on system design, validation, and performance optimization. To address these challenges, Keysight Technologies presents its forward-looking event, Engineering the Future of AI Systems—a technical deep dive into the tools,… Read More

The recent Chiplet Summit 2026 was a great place to learn about new chiplet designs, emerging standards, and a growing array of support technologies to help design and manufacture chiplet-based systems. In my travels at the show, I found a lot of technology that fit these descriptions. But there were also companies at the show that… Read More

Load-pull power amplifier (PA) design techniques determine the optimal impedances at the power transistor’s extrinsic reference plane, which is the physically accessible boundary for measurement or simulation. This reference plane can be the package transistor leads, die bond pads, or IC chip terminals. It includes… Read More

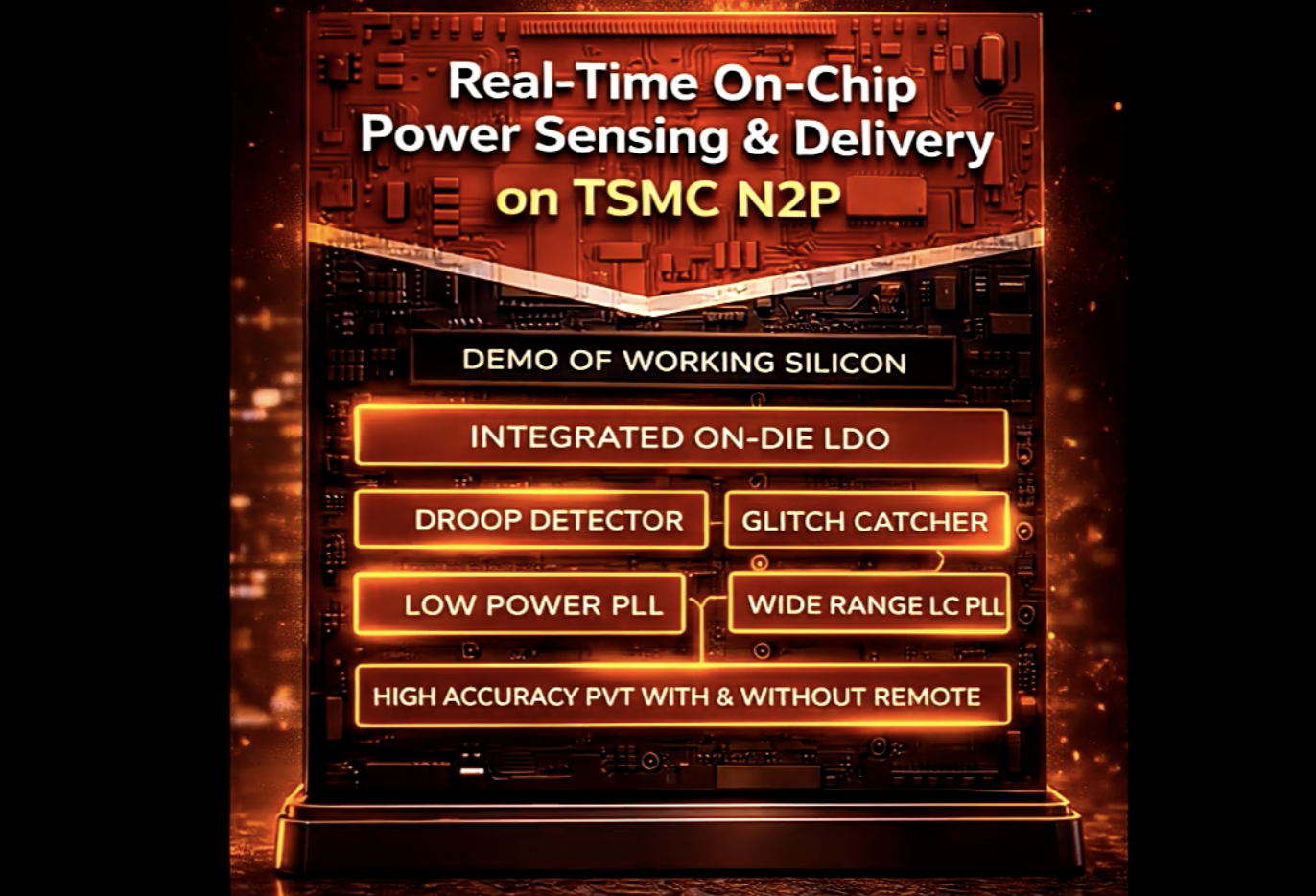

Analog Bits has a way of stealing the show at every event they attend. The formula is actually quite straight-forward – come to the show with the most relevant, highest impact IP running on the most advanced process. The company will be applying this strategy again at the upcoming TSMC 2026 Technology Symposium with an array of real-time… Read More

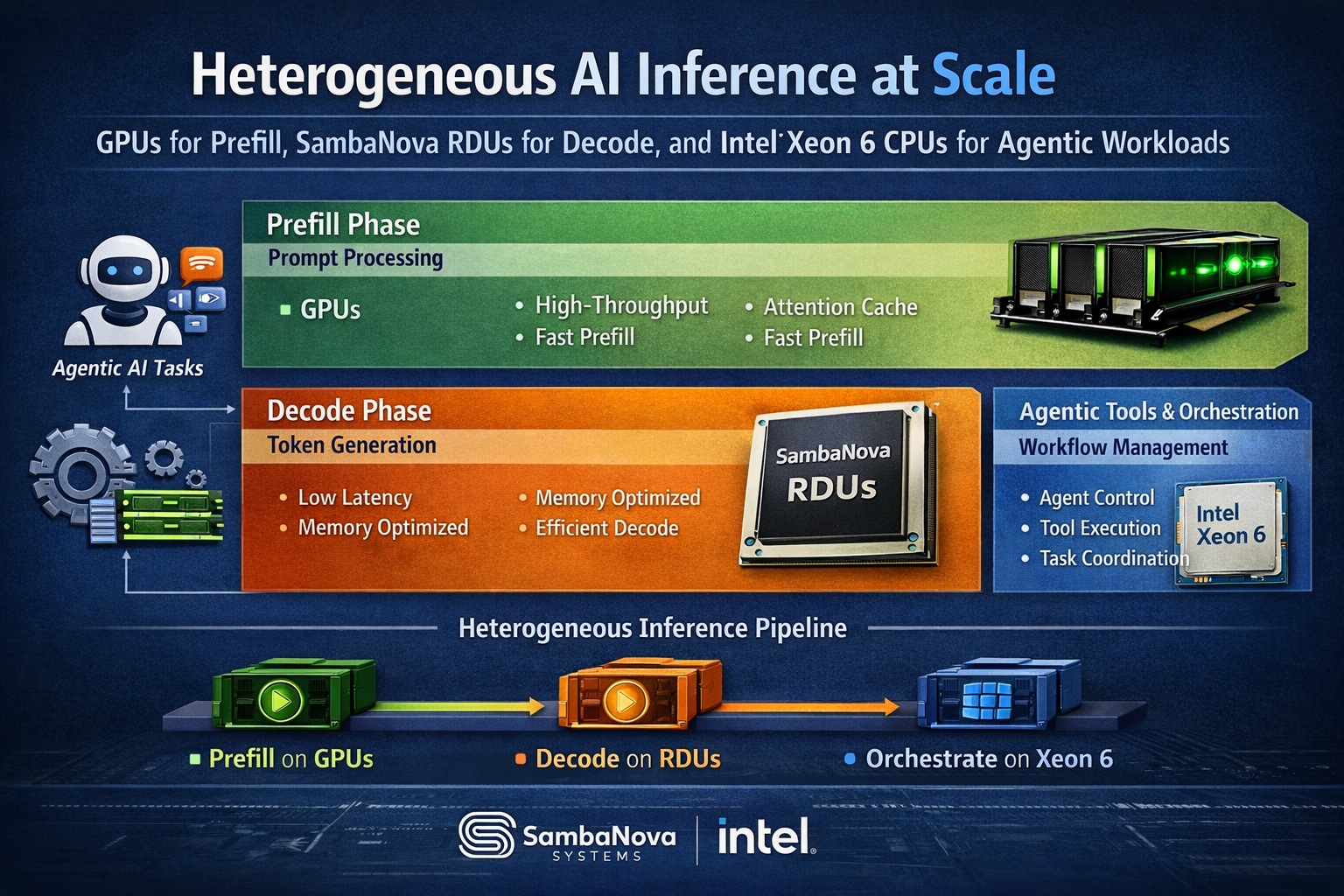

SambaNova Systems and Intel have introduced a blueprint for heterogeneous inference that reflects a significant shift in how modern large language model (LLM) workloads are deployed. Instead of relying on a single accelerator type, the proposed architecture assigns different phases of inference to specialized hardware:… Read More

With over two decades of experience bridging technology and business, Johan Wadenholt Vrethem focused on harnessing AI to transform how organizations operate and engage with their customers. After leading critical digital initiatives and client engagements in the banking and finance sectors at CGI, Johan co-founded Voxo… Read More

The opening of the TSMC 2026 earning call series brought no surprises. CC Wei has done more than 30 such calls since taking the CEO position in 2018 and he never fails to disappoint. Once again, CC Wei reported numbers above guidance driven by strong demand and flawless execution. This illustrates the benefit of TSMC’s close collaborations… Read More

Daniel is joined by Hezi Saar, Executive Director of Product Marketing at Synopsys, Hezi is responsible for the mobile, automotive, and consumer IP product lines. He brings more than 20 years of experience in the semiconductor and embedded systems industries.

Dan explores the growing field of physical AI with Hezi, who explains… Read More

How Time-Based Scheduling

Reclaims Silicon Wasted by Speculative Execution

By: Dr. Thang Tran, Founder and CTO, Simplex Micro

I have spent my career designing processor architectures, and I have reached an uncomfortable conclusion: a substantial fraction of the silicon area and power in modern high-performance processors… Read More

Is Intel About to Take Flight?