2024 DVCon was very busy this year. Bernard Murphy and I were in attendance for SemiWiki, he has already written about it. Multi die and chiplets was again a popular topic. Lauro Rizzatti, a consultant specializing in hardware-assisted verification, moderated an engaging panel, sponsored by Synopsys, focusing on the intricacies… Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

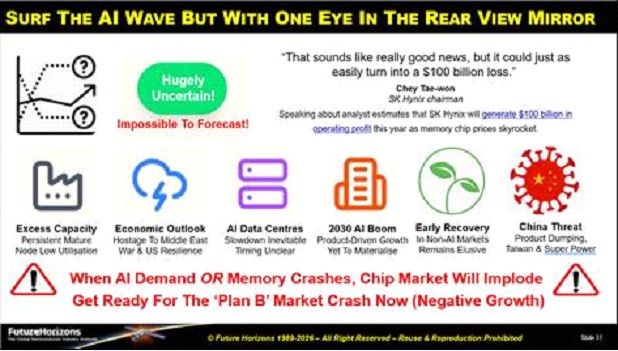

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MoreAndes Technology: Pioneering the Future of RISC-V CPU IP

On September 13, 2021, Andes Technology Corporation successfully issued its GDR (Global Depositary Receipt) public offering on the Luxembourg Stock Exchange. At the time it made Andes the only international public RISC-V Instruction set architecture (ISA) CPU IP supplier. This allowed investors around the world to participate… Read More

Podcast EP213: The Impact of Arteris on Automotive and Beyond with Frank Schirrmeister

Dan is joined by Frank Schirrmeister, vice president of solutions and business development at Arteris. He leads activities in the industry verticals including automotive and technology horizontals like artificial intelligence, machine learning, and safety. Before Arteris, Frank held senior leadership positions at Cadence… Read More

CEO Interview: Ganesh Verma, Founder and Director of MoogleLabs

A thought leader with demonstrated history in multiple roles- project life cycles, ideation, implementation, and closing projects delivering business value and delighting stakeholders, crafting technical aspects of the company’s strategy for aligning with the business goals perfectly, discovering and implementing … Read More

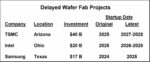

Semiconductor CapEx Down in 2024

U.S. President Biden announced on Wednesday an agreement to provide Intel with $8.5 billion in direct funding and $11 billion in loans under the CHIPS and Science Act. Intel will use the funding for wafer fabs in Arizona, Ohio, New Mexico, and Oregon. As reported in our December 2023 newsletter, the CHIPS Act provides a total of $52.7… Read More

2024 Outlook with John Lee, VP and GM Electronics, Semiconductor and Optics Business Unit at Ansys

We have been working with Ansys since SemiWiki was founded in 2011. It has been a richly rewarding relationship in all regards. I always say the semiconductor industry is filled with the most intelligent people in the world and Ansys is an excellent proof point. I have known John Lee for 30+ years and he is one of my trusted few, absolutely.… Read More

Simulating the Whole Car with Multi-Domain Simulation

Next significant automotive blog in a string I will be posting (see here for the previous blog).

In the semiconductor world, mixed simulation means mixing logic sim, circuit sim, virtual sim (for software running on the hardware we are designing) along with emulation and FPGA prototyping. While that span may seem all-encompassing,… Read More

QuantumPro unifies superconducting qubit design workflow

To create quantum computing chips today, a typical designer must cobble various tools together, switching back and forth between them for different tasks. By contrast, EDA solutions such as Keysight Advanced Design System (ADS) unify a design workflow in a single interface with automated data exchange between features. In … Read More

sureCore Enables AI with Ultra-Low Power Memory IP

We all know that AI is becoming pervasive in a wide array of products to make them smarter, safer and feature rich. Just look at the announcements from the recent CES show in Las Vegas to see some examples. These AI workloads demand a lot of compute power. Fueling this trend is the need for significant arrays of embedded memory on chip,… Read More

Challenge and Response Automotive Keynote at DVCon

Keynotes commonly provide a one-sided perspective of a domain, either customer-centric or supplier-centric. Kudos therefore to Cadence’s Paul Cunningham for breaking the mold in offering the first half of his keynote to Anthony Hill, a TI fellow, to talk about outstanding challenges he sees in verification for automotive … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior