On September 13, 2021, Andes Technology Corporation successfully issued its GDR (Global Depositary Receipt) public offering on the Luxembourg Stock Exchange. At the time it made Andes the only international public RISC-V Instruction set architecture (ISA) CPU IP supplier. This allowed investors around the world to participate in the growth Andes envisioned for RISC-V. This capital infusion would fuel Andes ambition to become a leader in the rapidly evolving, high-growth, open standard RISC-V market. In 2015 recognizing the vast potential for the RISC-V ISA, Andes had become a Founding and Premier Member of RISC-V International.

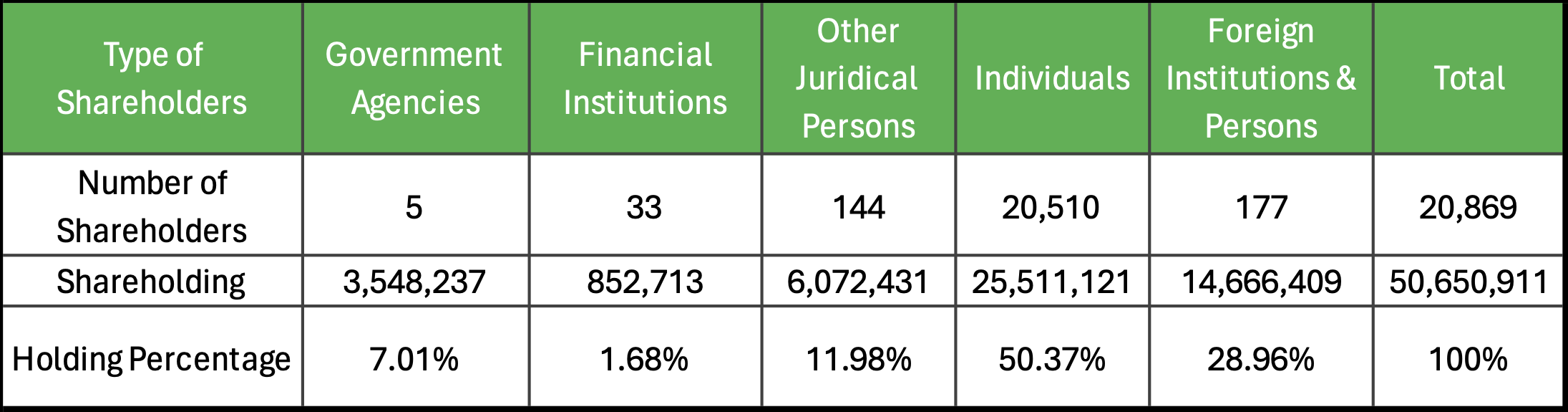

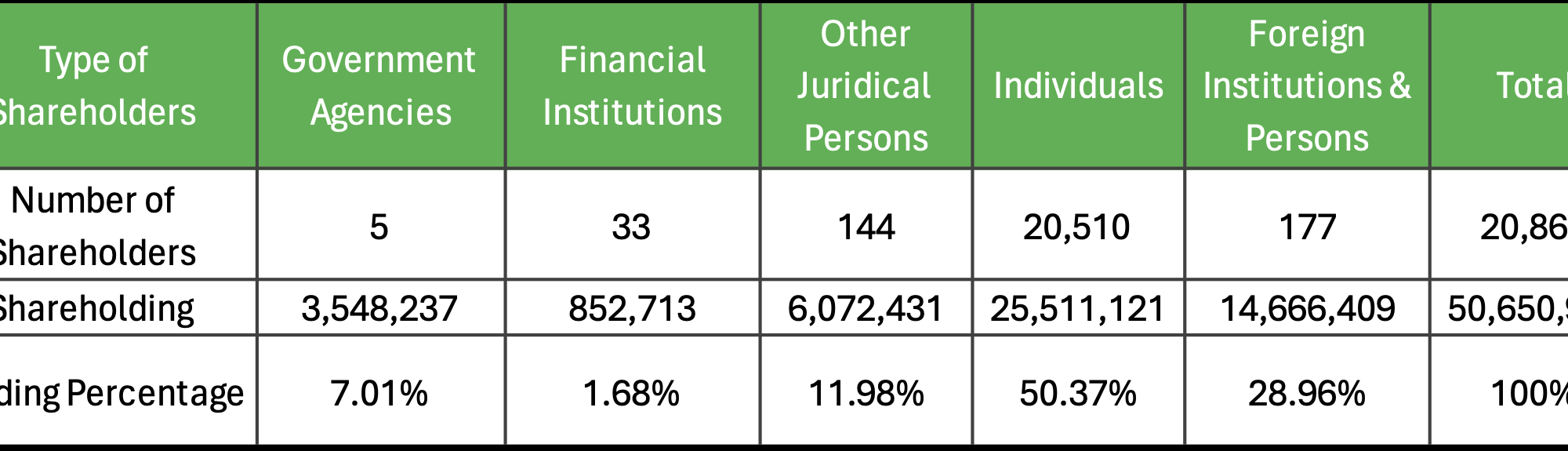

As of April 2, 2023; Unit: Shares %

The investment has paid off significantly particularly because it coincided with ratification of the RISC-V Vector Extension in November 2021. This event marked a turning point in the evolution of the RISC-V instruction set architecture. RISC-V vector extension came at a time when data center computing was changing from general purpose processing to AI processing, which handles extremely large data sets. Vector processing excels in efficient processing of large arrays or structured data. Vector processing has the potential to make RISC-V the next major worldwide ISA.

A vector processor’s highly parallel architecture reduces latency and overhead. It achieves better energy efficiency by maximizing CPU resource utilization and minimizing idle cycles, thus realizing higher performance per watt. Moreover, the hardware to implement RISC-V Vector processing units (VPUs) and vector registers is simpler than highly parallel architectures used for graphics processing. And VPUs provide a far less complex programming model.

The Andes R&D teams in both the North American operation and the expanded Taiwan staff have been focused on developing cutting-edge architectures for high-end RISC-V processors. Notably, the two achieved a significant milestone by developing the first RISC-V vector (RVV) engine, the AndesCore™ NX27V, based on the RISC-V International RVV specification. Showcasing the agility and innovation of the Andes engineering team, the design was completed within a year and based on version V0.8 of the RISC-V vector extension specification, and later on modified to version V1.0 when RVV was ratified. This accomplishment led to a few major OEM design wins.

Last year at the International Symposium on Computer Architecture (ISCA) 2023 conference in Orlando, Florida, META presented its paper, “MTIA: First Generation Silicon Targeting Meta’s Recommendation Systems,” which is the company’s data center, AI servers project. There are 64 processing elements (PE) in the server design that support MRETA’s custom-built proprietary accelerator. Each PE contains two processors: one scalar and one vector. Both are Andes IP that META engineers highly customized, using Andes Custom Extensions (ACE) to produce a completely unique solution targeted at META’s specific AI computing requirements.

The design validated the efficacy of RISC-V with Vector Extensions as a powerful solution to AI data center computing needs at a time when demand for data center processing hardware is exploding. According to Future Market Insights‘ report “Data Center CPU Market Outlook (2023 to 2033),” The data center CPU market is expected to grow significantly over the next few years, driven by the increasing demand for cloud computing, big data analytics, and artificial intelligence (AI). Key drivers of this growth include the need for faster data processing, increased efficiency, and reduced costs.

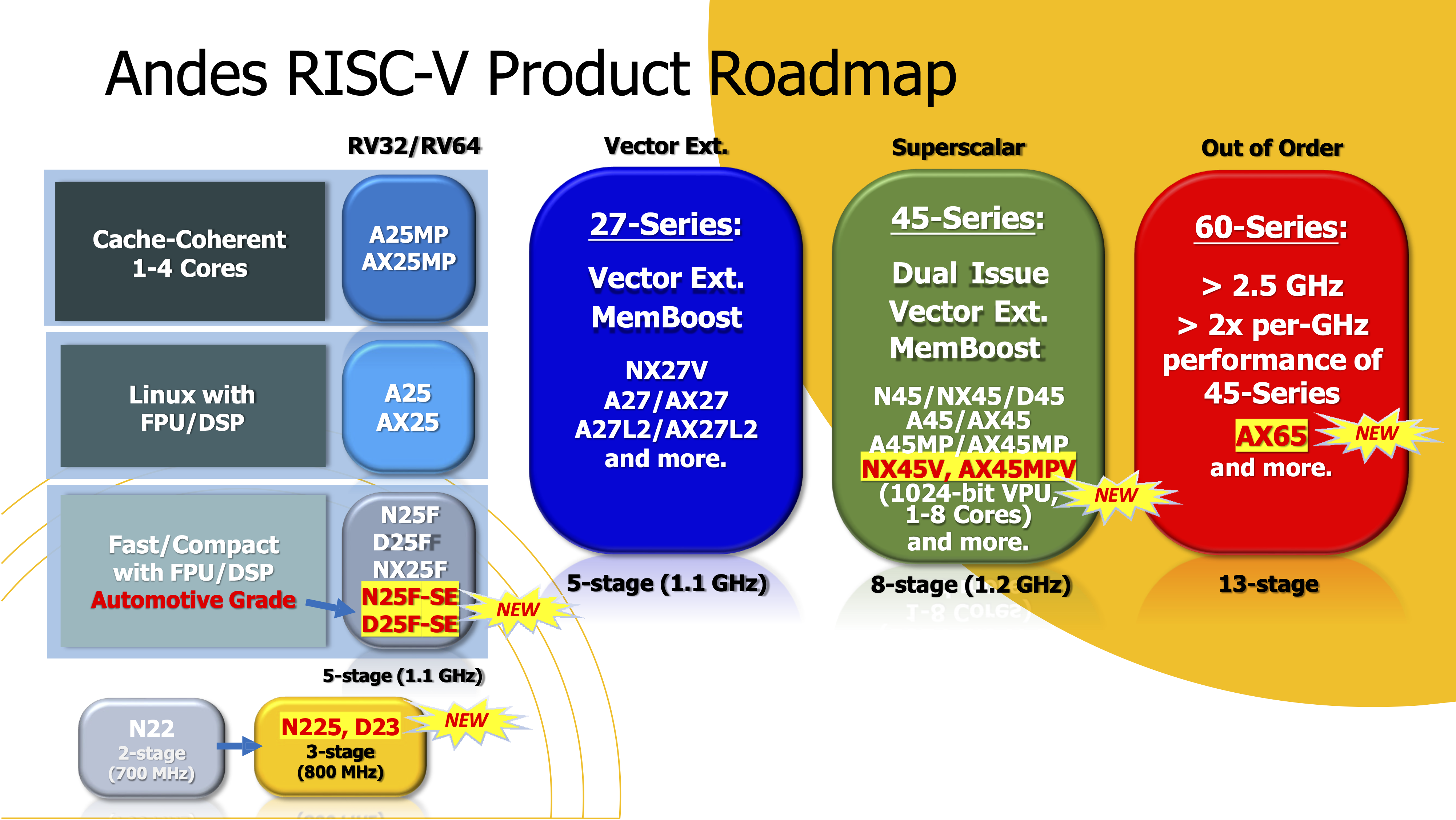

In 2021, in addition to vector extensions RISC-V International ratified 11 more extensions. Figure 1 illustrates the Andes product roadmap to support these extensions. Along the way to end of 2022 N25F-SE, 27 Series, and 45 series have since been delivered, in 2023, Andes delivered six new RISC-V cores to the market, such as D25F-SE, D23, N225, NX45V, AX45MPV as well as AX65. The road map spans from low-power and highly secured entry-level RISC-V processor AndesCore™ D23 to the AX65, the first in the 60 series, which was released in 2023 Q4 and is now shipping for customers designs.

The AX65 is a 13-stage, 4-way 64 bit out of order processor with RVA 22 profile (RVA22U64 profile specifies the ISA features available to user-mode execution environments in 64-bit applications processors). Equipped with 13-stage pipeline, 4-wide decode, 8-wide out-of-order execution, the series targets the Linux application processor sockets of computing, networking, and high-end controllers.

The AX65 allows multicore clusters from one to four to eight cores. The performance is world class, operating at 2.4 gigahertz clock frequency in seven nanometers TSMC process. The spec integers (Specint 2006) performance is 8.25 per gigahertz, and a SpecFp2006 is 10.2 per gigahertz, which are the best-known SPEC CPU® 2006 performance with two level cache design. The AX66, AX63 and AX67 will be delivered thereafter.

One other area Andes has made significant investment in is high performance automotive-grade RISC-V CPU IP. The penetration of RISC-V SoCs in automotive designs is projected to reach 21.4% by 2030, according to The SHD Group “RISC-V Market Report: Application Forecasts in a Heterogeneous World.” Andes developed functional safety-compliant products, include its N25F-SE, the world’s first fully ISO 26262 compliant RISC-V CPU IP; D25F-SE, which supports DSP extension instructions; and the 45-SE series processors that meet the highest ASIL level, ASIL D. ACE function will be enhanced to add support for 45-series processors.

On the strength of the demand Andes RISC-V products have experienced, the company continues to remain profitable and continues to enjoy rapid growth. From 2021 to 2023, Andes revenue showed nearly 30% growth. This was fueled by over 300 commercial licensees and over 600 signed license agreements with geographically distributed customers in Taiwan, China, Korea, Japan, Europe, and the USA. The company’s worldwide headcount grew nearly 70% over the same period.

Conclusion

In an era defined by rapid technological evolution, Andes Technology Corp. stands at the forefront of innovation in the RISC-V CPU IP market. From its pioneering issuance of overseas depositary receipts (GDR) to its groundbreaking advancements in RISC-V architecture, Andes Technology continues to redefine industry standards and shape the future of computing. As the demand for efficient, high-performance computing solutions continues to rise, Andes Technology remains committed to delivering unparalleled RISC-V solutions to drive transformative change across the global technology landscape.

Also Read:

LIVE WEBINAR: RISC-V Instruction Set Architecture: Enhancing Computing Power

WEBINAR: Leverage Certified RISC-V IP to Craft ASIL ISO 26262 Grade Automotive Chips

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.