The automotive industry imposes stringent requirements on Functional Safety. For semiconductor companies involved in automotive chips and even further upstream in Silicon Intellectual Property (SIP), obtaining ISO 26262 certification is a fundamental requirement for product penetration into automotive applications. Andes Technology is actively developing a portfolio of automotive-grade IP products to enhance the efficiency of product functional safety verification activities. One of the processors in the series, the A(X)25MP processors have ISO 26262 safety certification. The A(X)25MP, has a single instruction multiple data (SIMD) ISA that accelerates performance for signal processing operations common in a wide range of automotive computing requirements.

In addition to floating-point extensions, the 25-series processors are equipped with a 5-stage pipeline that is optimized for high operating frequency and high performance. They also feature instruction and data caches, local memories for low-latency accesses, and ECC for L1 memory soft error protection. The processors also provide branch prediction for efficient branch execution. Users can control power and energy consumption from multiple power management settings.

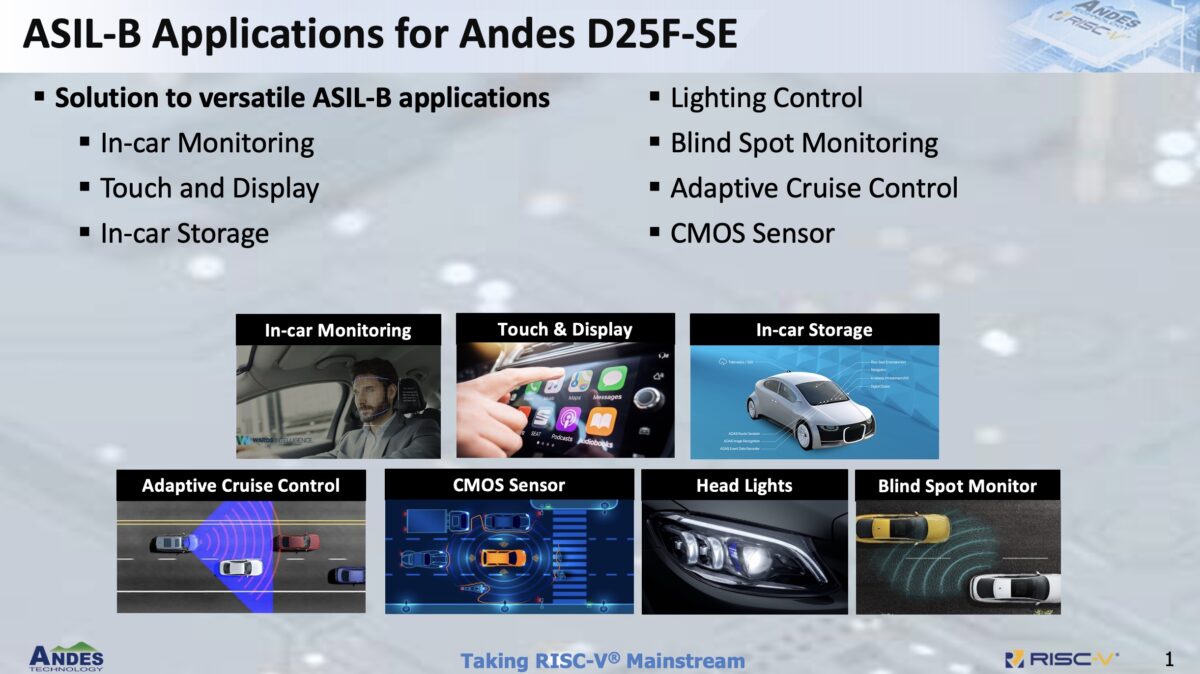

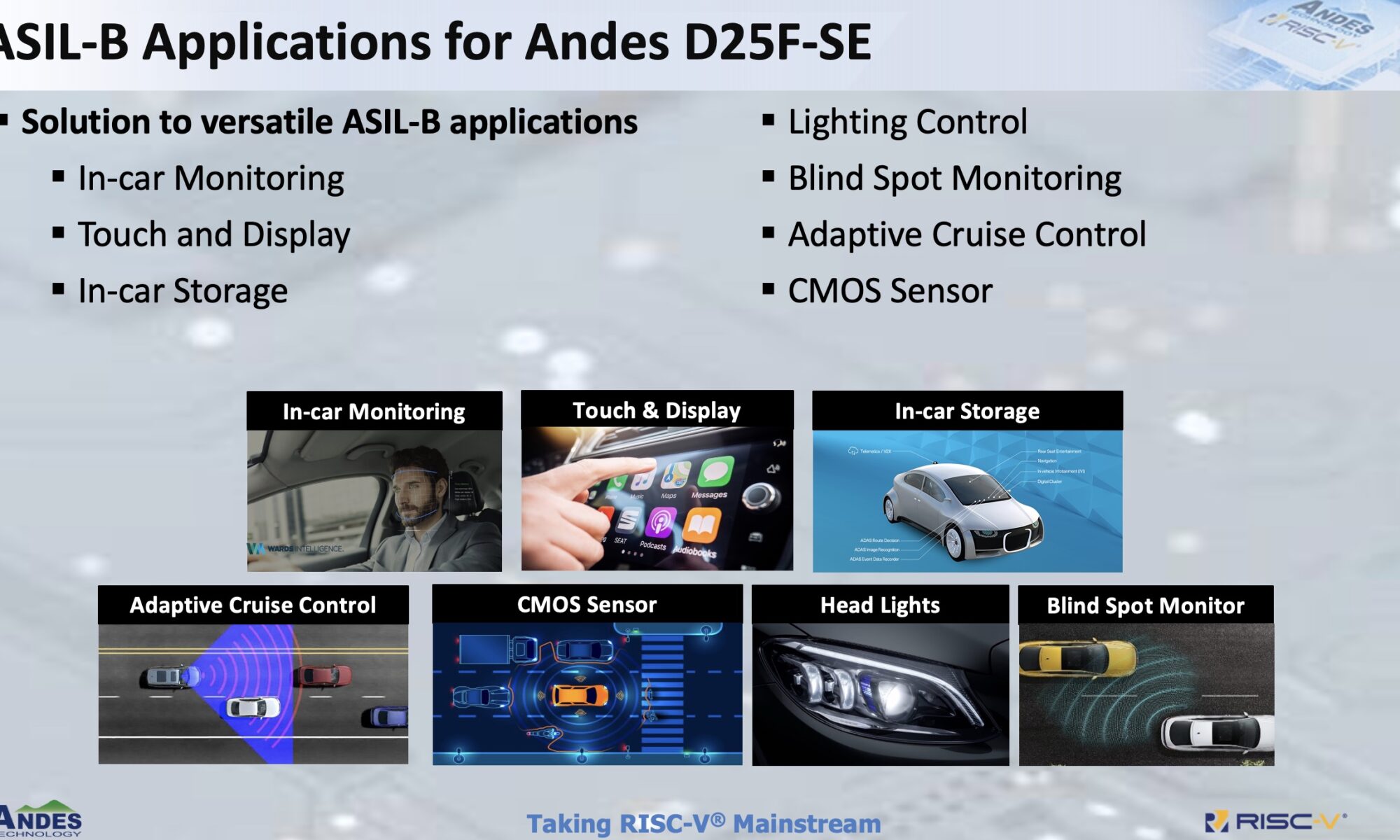

The company’s roadmap includes a comprehensive range of automotive IP products, covering RISC-V IP solutions with different functional safety levels from ASIL-B to ASIL-D, along with varying processor performance levels and feature sets. In 2023, Andes is set to officially introduce an 8-stage pipeline dual-issue processor that meets the ASIL-D standard. This signifies the company’s ability to provide tailored solutions for diverse automotive applications, highlighting their leading expertise in the automotive RISC-V IP market.

But a complete solution demands that a compute platform has a software tool chain that also meets the stringent requirements of the automotive world. That requirement is being met by long time Andes partner Green Hills Software. The adoption of the RISC-V instruction set architecture is increasing rapidly in countless markets, particularly automotive applications. The Green Hills ASIL certified µ-velOSity RTOS, advanced debugger and optimizing C/C++ compilers allow designers to efficiently create and confidently deploy safety- and security-critical RISC-V applications.

The µ-velOSity RTOS offers a clear and concise application programming interface (API) that shortens the development cycle. Kernel features supported in the RTOS include resource allocation. TCP/IP, MS/DOS, USB device/mass storage class, and embedded graphics. µ-velOSity can be used in on-chip memory, providing users with a faster execution speed and eliminating the need for off-chip memory. Faster execution speed together with quick boot time makes the software a useful solution in automotive applications.

The µ-velOSity RTOS is the smallest of Green Hills Software’s family of real-time operating systems. It has been updated and optimised to support the RISC-V architecture and has been certified to meet a broad number of industry standards for functional safety and security. Its streamlined design, coupled with seamless integration with the safety-certified Green Hills MULTI® integrated development environment (IDE) and C/C++ compilers, makes it easy to learn and use, allowing developers to create advanced solutions with the highest performance and smallest footprint for automotive, industrial, and IoT applications.

Also Read:

CEO Interview: Frankwell Lin, Chairman and CEO of Andes Technology

Pairing RISC-V cores with NoCs ties SoC protocols together

Deeper RISC-V pipeline plows through vector-scalar loops

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.