The EDA CEO outlook took an interesting turn last night but before I get into that I will offer a few comments about the start of the show. I attend this event every year for the content but also for the networking. It isn’t everyday you get to hang out with semiconductor industry elite and have candid conversations over food and drinks.… Read More

Agentic AI and the EDA Revolution: Why Data Mobility, Security, and Availability Matter More Than EverThe EDA (Electronic Design Automation) and semiconductor industries…Read More

Agentic AI and the EDA Revolution: Why Data Mobility, Security, and Availability Matter More Than EverThe EDA (Electronic Design Automation) and semiconductor industries…Read More WEBINAR: What It Really Takes to Build a Future-Proof AI Architecture?Keeping up with competitors in many computing applications…Read More

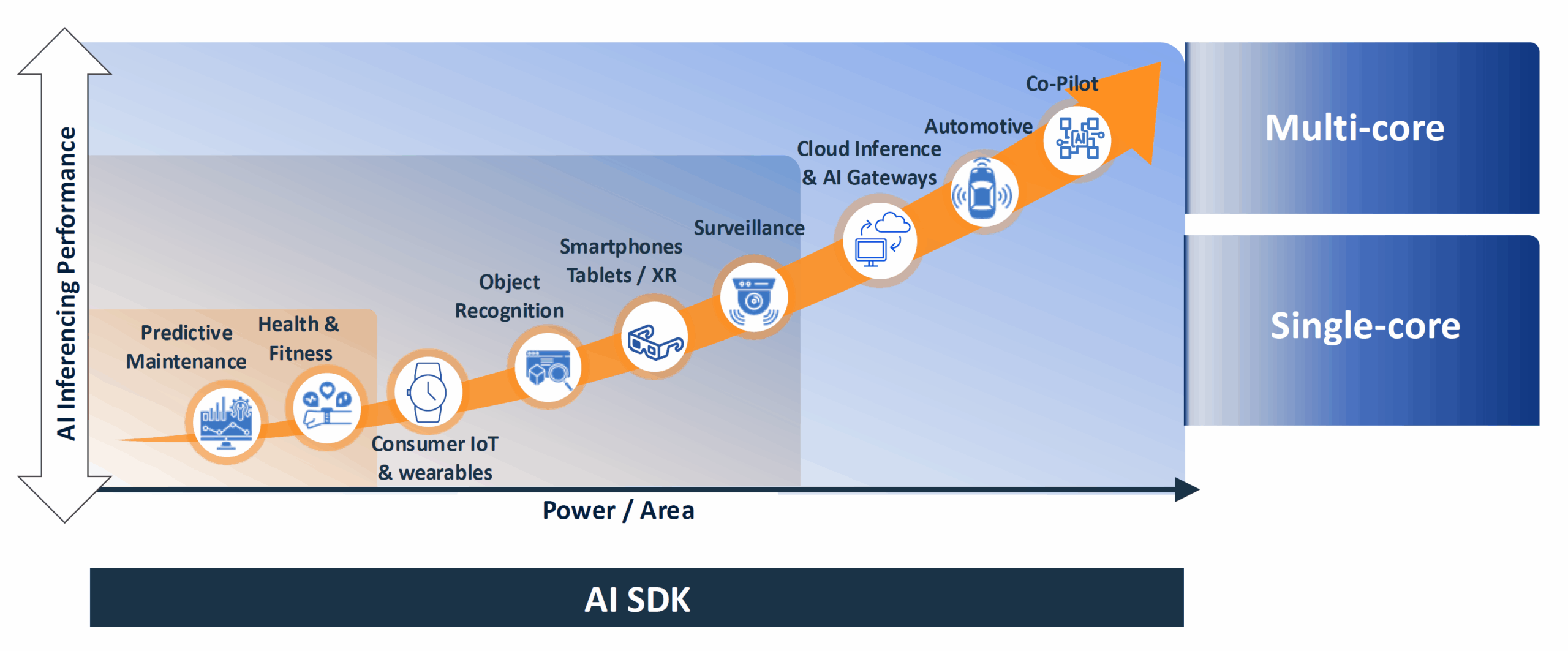

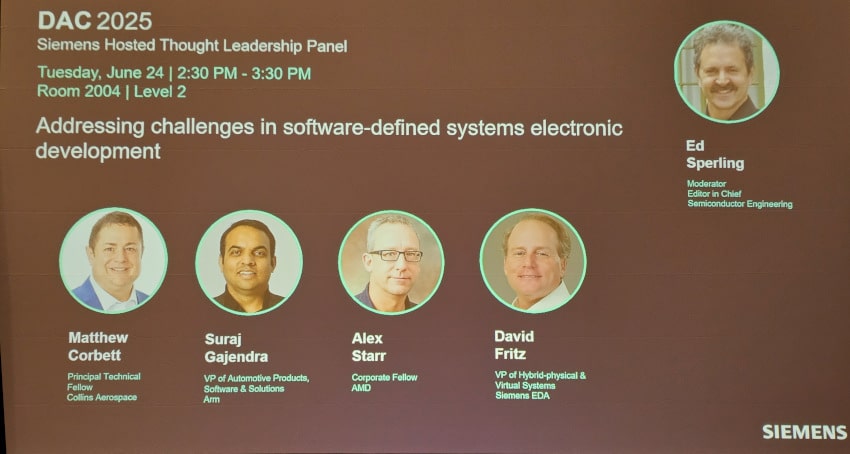

WEBINAR: What It Really Takes to Build a Future-Proof AI Architecture?Keeping up with competitors in many computing applications…Read More Software-defined Systems at #62DACModern EVs are prime examples of software-defined systems,…Read More

Software-defined Systems at #62DACModern EVs are prime examples of software-defined systems,…Read MoreThe 4th Way Beyond Simulation, FPGA Synthesis, and Emulation

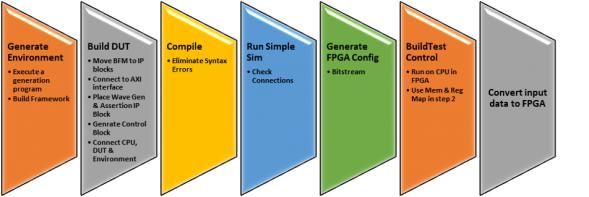

As verification continues to be a key ingredient in successful design implementation, new approaches have been tried to balance cost, time to results and comprehensive analysis in designs that require large patterns in some application like Image Processing. Simulation environments are well proven, and designers tend to … Read More

Stress and Aging

These failings aren’t just a cross we humans bear; they’re also a concern for chips, particularly in electrical over-stress (EOS) and aging of the circuitry. Such concerns are not new, but they are taking on new urgency given the high reliability and long lifetime expectations we have for safety-critical components in cars and… Read More

Mentor Leads Emulation Innovation

Publishing eBooks on FPGA Prototyping and Emulation really was an eye opener for me as a long time EDA and IP professional. Both markets are considered EDA in the traditional sense but they are very much in the systems business with a lot of IP. Both markets are also growing very rapidly and operate side-by-side with complimentary… Read More

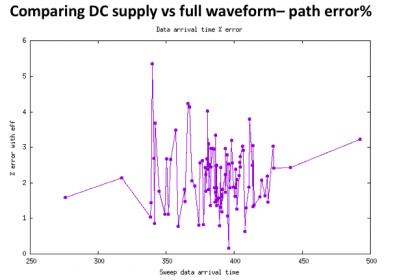

A New Problem for High-Performance Mobile

About 6 months ago, ANSYS was approached by a couple of leading mobile platform vendors/suppliers with a challenging problem. These companies were hitting target 2.5GHz performance goals on their (N10 or N7) application processors, but getting about 10% lower yield than expected, which they attributed to performance failures.… Read More

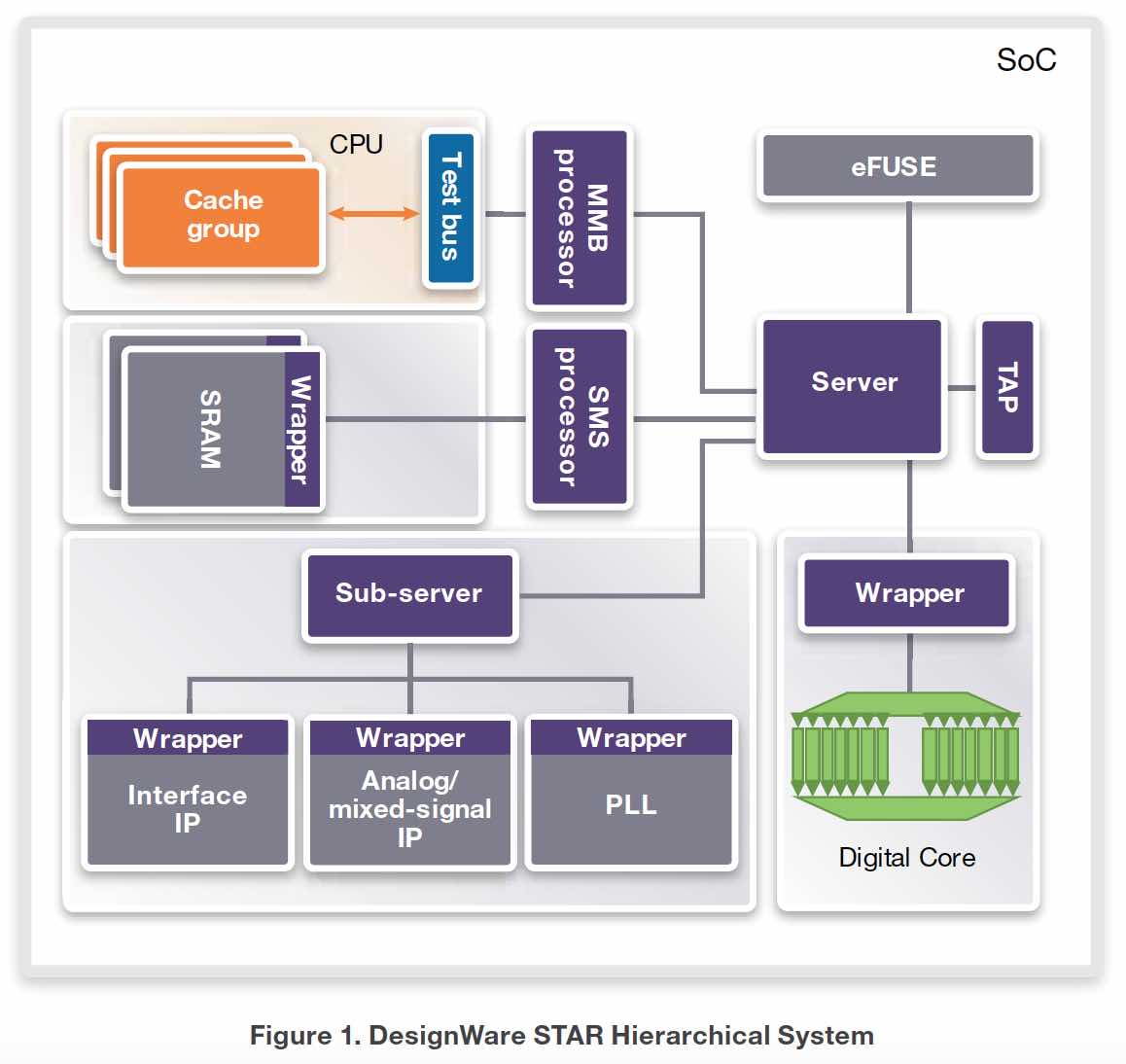

Safety Critical Applications Require Onboard Aging Monitoring

When it comes to safety, ISO 26262 is the spec that comes to mind for many people. However, there are layers of specifications that enable the level of safety required for automotive and other systems that need high reliability. For any application requiring safety, test is a critical element. A key spec for SOC test is IEEE 1500, … Read More

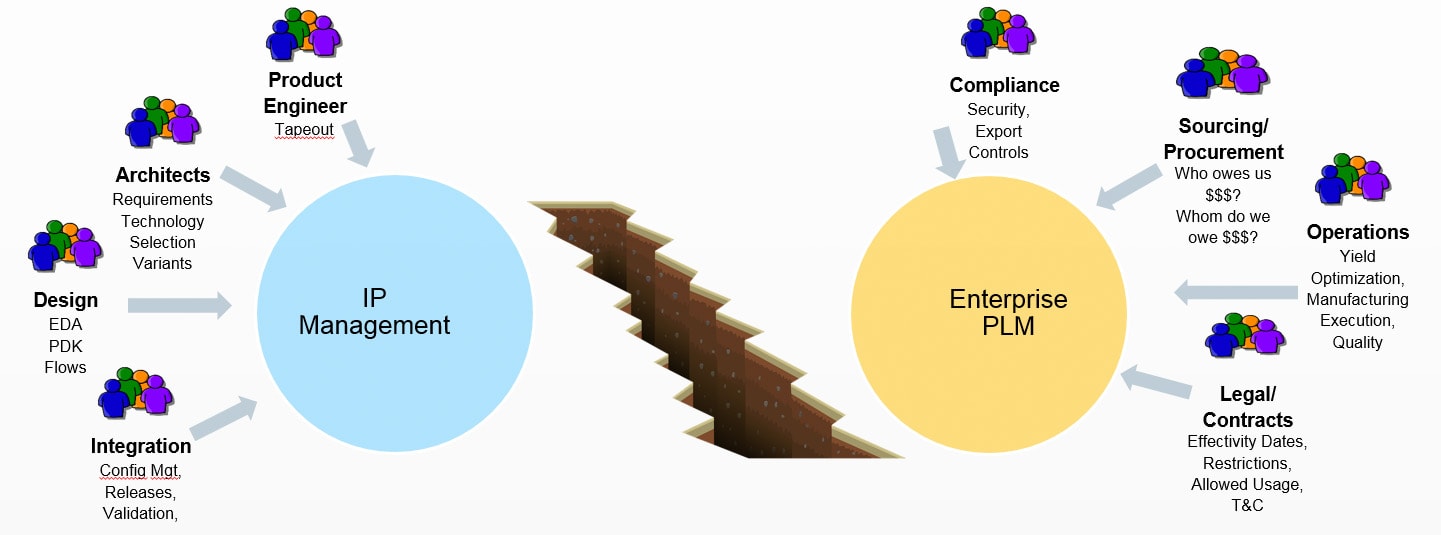

Combining IP and Product Lifecycle Tools

No single EDA company provides all of the tools needed to define requirements, design exploration, track IP, simulate, manage and verify a complex SoC system, so it makes sense that EDA vendors and point tool companies have tools that work together to achieve all of these difficult tasks. Systems design has been around for decades… Read More

Functional Safety Methodologies for Automotive Applications

During Q&A session at San Jose GTC 2018, nVidia CEO Jen-Hsun Huang reiterated that critical functional safety, such as in autonomous vehicle, requires both the redundancy and the diversity aspects. For example, CUDA with Tensor core and GPU with DLA were both utilized. Safety is paramount to automotive applications. Any… Read More

Tutorial on Advanced Formal: NVIDIA and Qualcomm

I recently posted a blog on the first half of a tutorial Synopsys hosted at DVCon (2018). This blog covers the second half of that 3½ hour event (so you can see why I didn’t jam it all into one blog :D. The general theme was on advanced use models, the first half covering use of invariants and induction and views from a Samsung expert on efficient… Read More

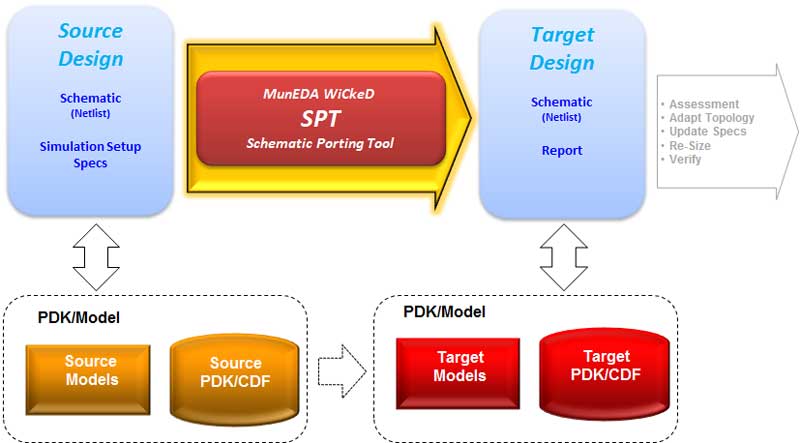

Schematic porting – the key to analog design reuse

At the beginning of every project the one of the first questions that ought to be asked is whether there blocks from previous designs that can be reused. On the surface this seems pretty obvious. The wrinkle in this is that reusability varies a lot based on the design type and the effort that a team is willing to expend to bring a design… Read More

Should Intel be Split in Half?