I commented recently on limitations in deep learning (DL), one of which is the inability to incorporate prior knowledge, like basic laws of mathematics or physics. Typically, understanding in DL must be inferred from the training set, which in a general sense cannot practically cover prior knowledge. Indeed one of the selling… Read More

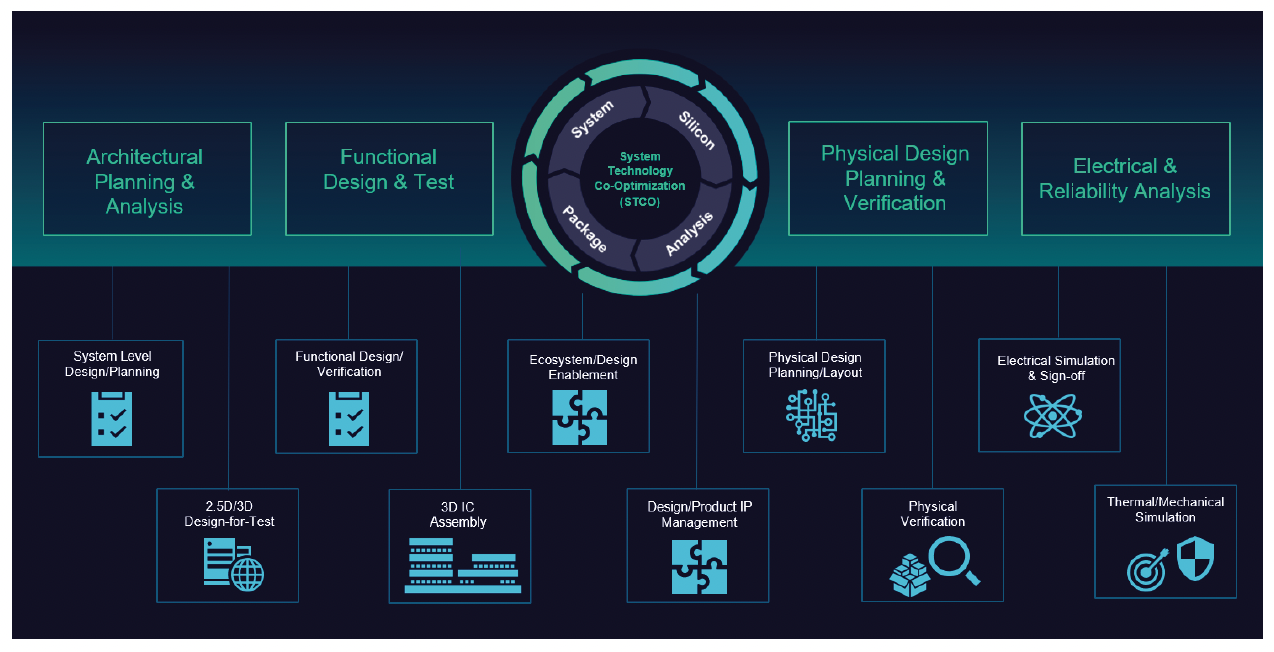

Enabling the Ecosystem for True Heterogeneous 3D IC DesignsThe demand for higher performance, greater configurability, and…Read More

Enabling the Ecosystem for True Heterogeneous 3D IC DesignsThe demand for higher performance, greater configurability, and…Read More Why I Think Intel 3.0 Will SucceedProbably one of the most anticipated semiconductor investor…Read More

Why I Think Intel 3.0 Will SucceedProbably one of the most anticipated semiconductor investor…Read More Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More

Griffin Securities’ Jay Vleeschhouwer on EDA Acquisitions and StartupsJay Vleeschhouwer, Managing Director of Software Research at…Read More Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More

Security Coverage: Assuring Comprehensive Security in Hardware DesignAs hardware systems become increasingly complex and security…Read More Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read More

Scaling 3D IC Technologies – Siemens Hosts a Meeting of the Minds at DAC3D IC was a very popular topic at…Read MoreEnhancing Early Static FSM

Finite state machines (FSMs) are widely adopted as part of reactive systems to capture their dynamic behaviors using a limited number of modes or states that usually change according to the applied circumstances. Some terminologies are frequently used to describe the FSM characteristics: state, transition, condition and … Read More

Tesla Leap of Faith (or the Adoration of Elon Musk)

The Reverend Elon Musk, CEO of Tesla Motors, held forth to his flock on yesterday’s earnings call. Musk described at length his efforts to lead the company out of production hell. The lengthy session highlighted the challenges facing the company, which posted its greatest quarterly loss ever, and was emblematic of the typical … Read More

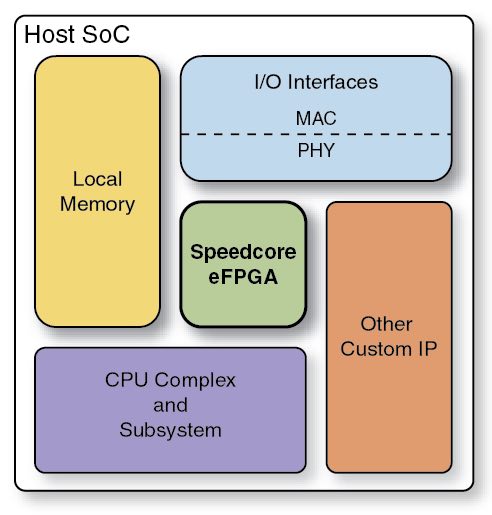

Timing Closure Techniques for SOCs with Embedded FPGA Fabric

Once the benefits of using an embedded FPGA fabric are understood, the next question is about how timing closure is handled between the ASIC and the eFPGA blocks. First let’s look briefly at the advantages. By moving the eFPGA on to the SOC die, tons of I/O logic and the need for any package and board interconnect will vanish. Package… Read More

Timing Channel Attacks are Your Problem Too

You’ve heard about Meltdown and Spectre and you know they’re really bad security bugs (in different ways). If you’ve dug deeper, you know that these problems are related to the speculative execution common in modern processors, and if you dug deeper still you may have learned that underlying both problems are exploits called timing… Read More

Cadence Update on AMS Design and Verification at #55DAC

As a blogger in the EDA industry I get more invitations to meet with folks at DAC than I have time slots, so I have to be a bit selective in who I meet. When the folks at Cadence asked me to sit down and chat with Mladen Nizic I was intrigued because Mladen is so well-known in the AMS language area and he’s one of the authors of, The Mixed-Signal… Read More

Synopsys Offers First Single-Vendor Comprehensive Photonic IC Design Flow

Synopsys has a long history of being a thought leader and it’s not surprising to see the company jumping into the forefront of new technologies. For decades, I’ve been steeped in electronic IC design and it caught me by surprise to find that Synopsys had been quietly working on filling out their portfolio in the optical design solutions… Read More

Career Change Advice and how EDA Hiring has Changed

I think most of us can attest that changing jobs is one of the most stressful decisions we make, as our careers progress. Making a job change is rarely an easy decision, though admittedly, so wonderful when it accomplishes your career and life goals. Having the right, well thought out expectations is the best way to ensure success,… Read More

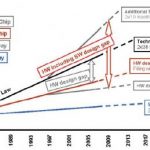

An update on the Design Productivity Gap

Over a decade ago, a group of semiconductor industry experts published a landmark paper as part of the periodic updates to the International Technology Roadmap for Semiconductors, or ITRS for short (link). The ITRS identified a critical design productivity gap. The circuit capacity afforded by the Moore’s Law pace of technology… Read More

Speak N Spell

This is the ninth in the series of “20 Questions with Wally Rhines”

Success has many authors and the Speak & Spell product from Texas Instruments generated lots of write-ups to demonstrate this. For most of the semiconductor industry, results of innovation were not apparent to the masses but, for the consumer … Read More

Musk’s new job as Samsung Fab Manager – Can he disrupt chip making? Intel outside