Arthur Hanson

Well-known member

Any thoughts or insights on this would be appreciated.

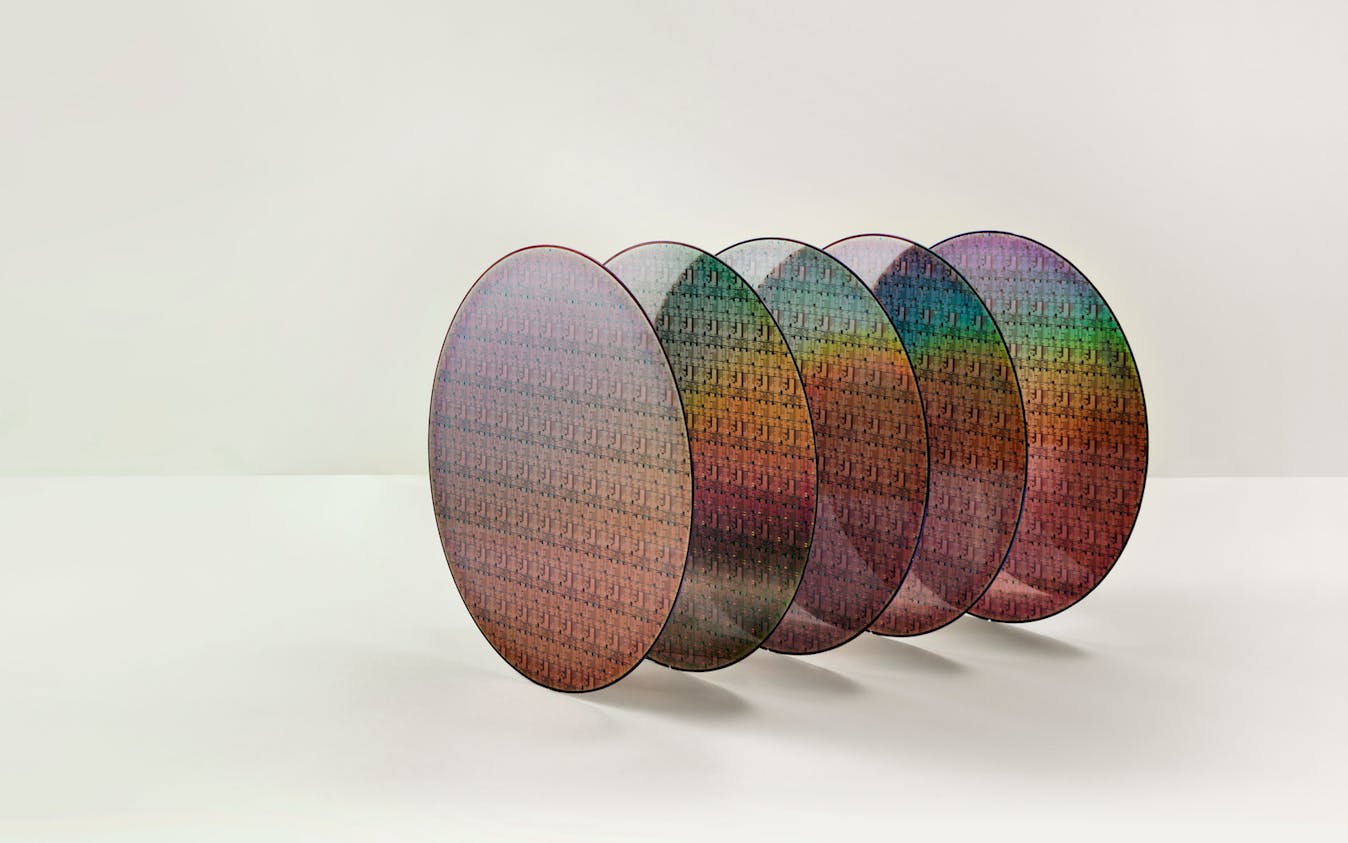

The global semiconductor chip shortage has led to significant frustration as organizations across many industries have resorted to plan B. However, it has also prompted significant investment in research and development efforts necessary to find new solutions.

Case in point – IBM and Samsung Electronics are jointly announcing a breakthrough that defies conventional semiconductor design and aims to reduce the energy usage of chips by 85 percent or double performance compared to scaled finFET transistors.

Developed by a joint team of researchers at the Albany Nanotech Complex, IBM and Samsung's new VTFET design prototype successfully implements transistors built vertically on the surface of a chip. Because transistors have, until now, been built horizontally to lie flat upon the surface of a semiconductor, this allows an exponential number of transistors to exist on a chip and removes density and energy efficiency constraints.

IBM and Samsung announce semiconductor design breakthrough

The global semiconductor chip shortage has led to significant frustration as organizations across many industries have resorted to plan B. However, it has also prompted significant investment in research and development efforts necessary to find new solutions.

Case in point – IBM and Samsung Electronics are jointly announcing a breakthrough that defies conventional semiconductor design and aims to reduce the energy usage of chips by 85 percent or double performance compared to scaled finFET transistors.

Developed by a joint team of researchers at the Albany Nanotech Complex, IBM and Samsung's new VTFET design prototype successfully implements transistors built vertically on the surface of a chip. Because transistors have, until now, been built horizontally to lie flat upon the surface of a semiconductor, this allows an exponential number of transistors to exist on a chip and removes density and energy efficiency constraints.