Pat has certainly brought more transparency, which I do appreciate. He still seems to be struggling with the Intel specific terminology though:

"We've got past some of the stumbles at 10 and now 7, and the daily updates that we're getting on wafers coming out of fab, the full embrace of EUV, we're very confident that we have that back on track. In fact, right now, we're taping out the compute tile, the Meteor Lake compute tile, is finishing tape-in as we speak," Gelsinger said.

He meant taping-in, which, as I have found, is an IDM terminology dating back to RCA Microelectronics in the 1970s. Us fabless people call it taping-out because we don't do the prep work for mask shops etc...

"The -- well publicized 7 nanometer stumbling, that's back on track, even embrace the EUV and I've set out a yearly cadence of process improvements. Also, we've restored our Tick-Tock product and core cadence."

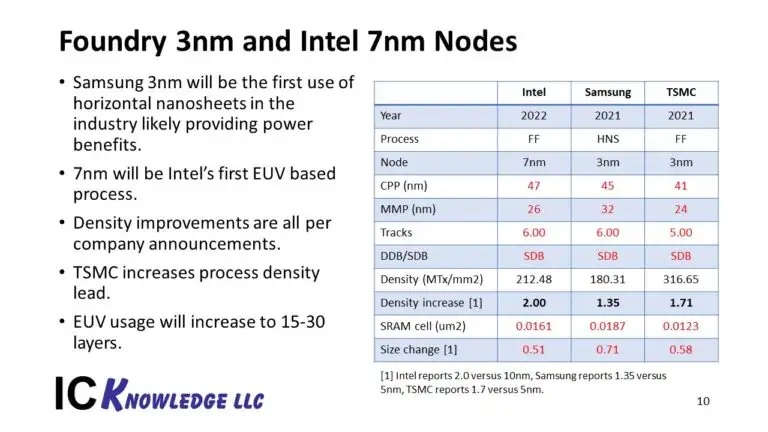

Intel invested a record amount in ASML for what we all thought would be early EUV access yet TSMC and Samsung had EUV in production first. Hopefully Pat will fix this. I do think Pat is a bit overly optimistic on Intel 7nm but I will give him the benefit of the doubt. The preliminary density numbers puts Intel 7nm between TSMC N5 and N3 but a year later than TSMC N3 for risk production. TSMC N5 started risk production in 2019.

"We do see that Q1 was approximately the bottom for the data center business and we're now on a solid path of recovery."

It was the bottom for Intel but the top for AMD? This competition just got interesting.

"And I do feel in that, hey, not everything -- years of bad decisions don't get fixed, because you got some new exciting CEO coming in."

Very true. Go Pat go!

" You don't want all of your eggs in the basket of a Taiwan fab, right, given some of the geopolitical situation, just supply chain resilience management post COVID, right. You want to look at your second supplier alternatives as well."

He is not wrong which is why Samsung is important and yes it would be great to have a third foundry alternative, absolutely. I was hoping for more color on the TSMC relationship but hopefully that will come sooner rather than later.

"We've got past some of the stumbles at 10 and now 7, and the daily updates that we're getting on wafers coming out of fab, the full embrace of EUV, we're very confident that we have that back on track. In fact, right now, we're taping out the compute tile, the Meteor Lake compute tile, is finishing tape-in as we speak," Gelsinger said.

He meant taping-in, which, as I have found, is an IDM terminology dating back to RCA Microelectronics in the 1970s. Us fabless people call it taping-out because we don't do the prep work for mask shops etc...

"The -- well publicized 7 nanometer stumbling, that's back on track, even embrace the EUV and I've set out a yearly cadence of process improvements. Also, we've restored our Tick-Tock product and core cadence."

Intel invested a record amount in ASML for what we all thought would be early EUV access yet TSMC and Samsung had EUV in production first. Hopefully Pat will fix this. I do think Pat is a bit overly optimistic on Intel 7nm but I will give him the benefit of the doubt. The preliminary density numbers puts Intel 7nm between TSMC N5 and N3 but a year later than TSMC N3 for risk production. TSMC N5 started risk production in 2019.

"We do see that Q1 was approximately the bottom for the data center business and we're now on a solid path of recovery."

It was the bottom for Intel but the top for AMD? This competition just got interesting.

"And I do feel in that, hey, not everything -- years of bad decisions don't get fixed, because you got some new exciting CEO coming in."

Very true. Go Pat go!

" You don't want all of your eggs in the basket of a Taiwan fab, right, given some of the geopolitical situation, just supply chain resilience management post COVID, right. You want to look at your second supplier alternatives as well."

He is not wrong which is why Samsung is important and yes it would be great to have a third foundry alternative, absolutely. I was hoping for more color on the TSMC relationship but hopefully that will come sooner rather than later.