Whether we realize it or not, everyday applications we use depend on data gathered by sensors. We can bet that pretty much every application uses at least a couple of different types of sensors, if not more. That is because different types of sensors are better suited to collect data depending on the application, the environment from which data is to be gathered, whether it is daytime or night, etc. Many times, many different types of sensors are used to gather data for the same application because depending on just one may be unreliable. This is where the concept of sensor fusion comes in. Sensor fusion means combining data from multiple sensors to obtain complete, accurate and reliable results. It enables context awareness and new user experiences.

This process relies on lot of processing algorithms and is very taxing on the software. Of course, hardware doesn’t have a cake walk in this respect. More times than not, the algorithms have to be implemented in a special purpose chip rather than running on a general purpose processor. The ever present demanding requirements of PPA pushes applications to implement sensor fusion in an optimized hardware/software solution.

Recently, Synopsys hosted a webinar titled “DSP IP for High Performance Sensor Fusion on an Embedded Budget.” The keywords in the title are “embedded” and “budget”. As we all recognize, many of the fast growing applications of today are embedded in nature. These applications demand very high performance, compact implementation and low power consumption. At the same time, the business requirements are even tighter in terms of price points and time to market expectations.

This post covers some salient points from the webinar. You may already be part of a team that is implementing a sensor fusion solution for an end application among the many that depend on multiple sensors. Or you may soon be. Irrespective, this webinar is a very useful one for you to watch. Pieter van der Wolf, Principal R&D Engineer at Synopsys presented the webinar. It is available for viewing on-demand here.

Sensor Fusion Trends

Smart mobile, automotive systems, smart home systems, health and industrial control are some of the markets leveraging and benefitting from the use of multiple sensors. MEMS technology for miniaturization and the lower cost of sensors are rapidly fueling the innovations in the sensor fusion space. At the same time, the requirements for even a pedometer application covers a wide range of sensors. The use of different sensors in wearables to virtual assistants to automotive radar/LiDAR – requires SoCs to have an optimal balance of performance and low power/area. As no single type of sensor is perfect for every application, sensor fusion is key for accurate and reliable results. The key tasks of sensor fusion includes localization, mapping and path planning. Localization is to determine the “where am I?” component. Mapping is to determine the “what’s around me?” based on the model of expected environment with objects and their properties. And the Path Planning is to determine the “what to do next?” action decision.

DSP IP for Sensor Fusion Solutions

SoC architectures must be able to scale easily with fast changing requirements from applications. The SoCs must also be versatile enough to handle varying workloads and data types. Building from scratch for every new variant or future version of a product is not practical. A DSP lends itself nicely to accommodate these requirements.

Scalability

A pedometer application requires about 10 MIPS while an autonomous driving application needs 10 TOPS or higher. A scalable, software-compatible family of DSP IP can serve well to implement a range of sensor fusion applications, while enabling re-use of the software across all these SoCs.

Versatility

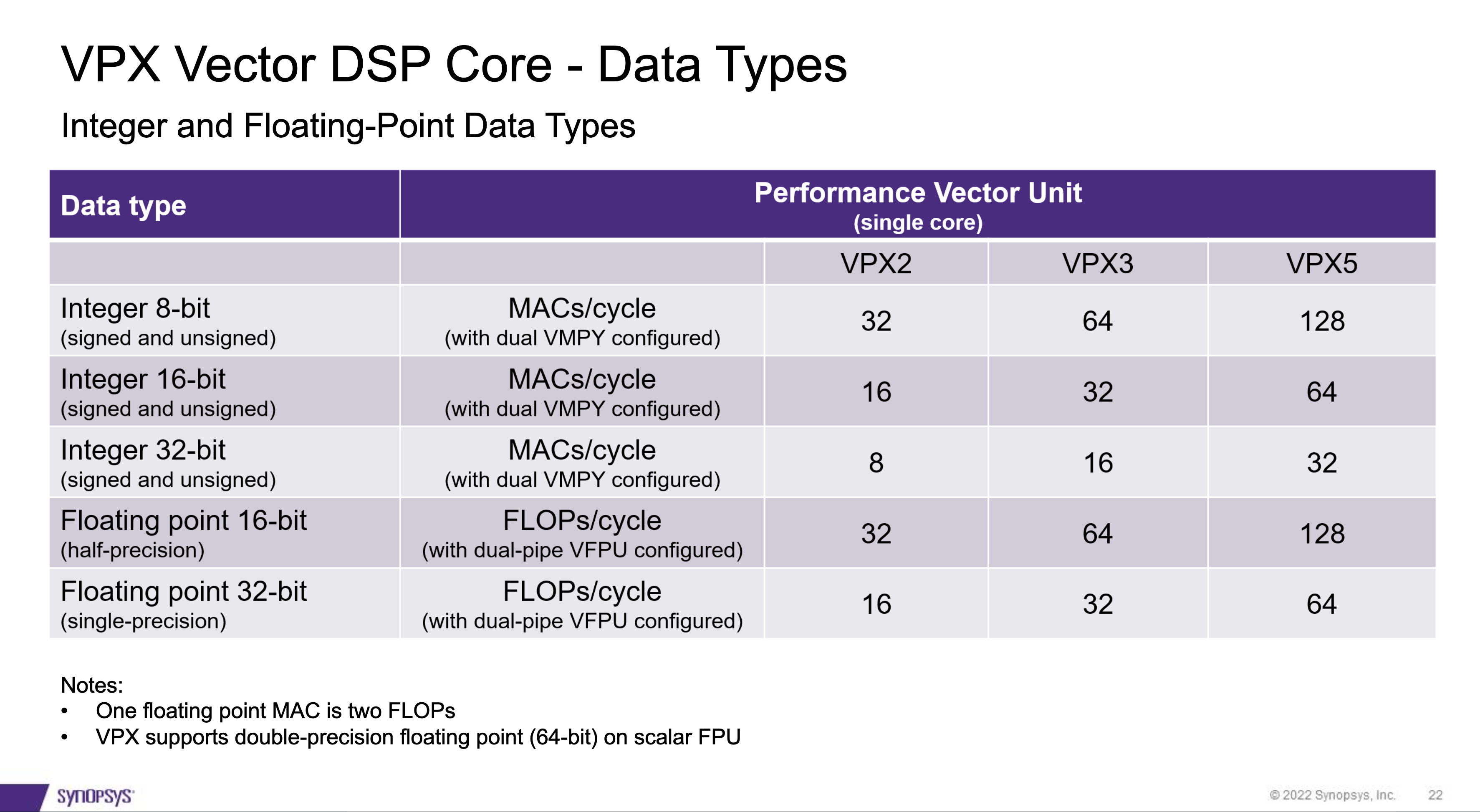

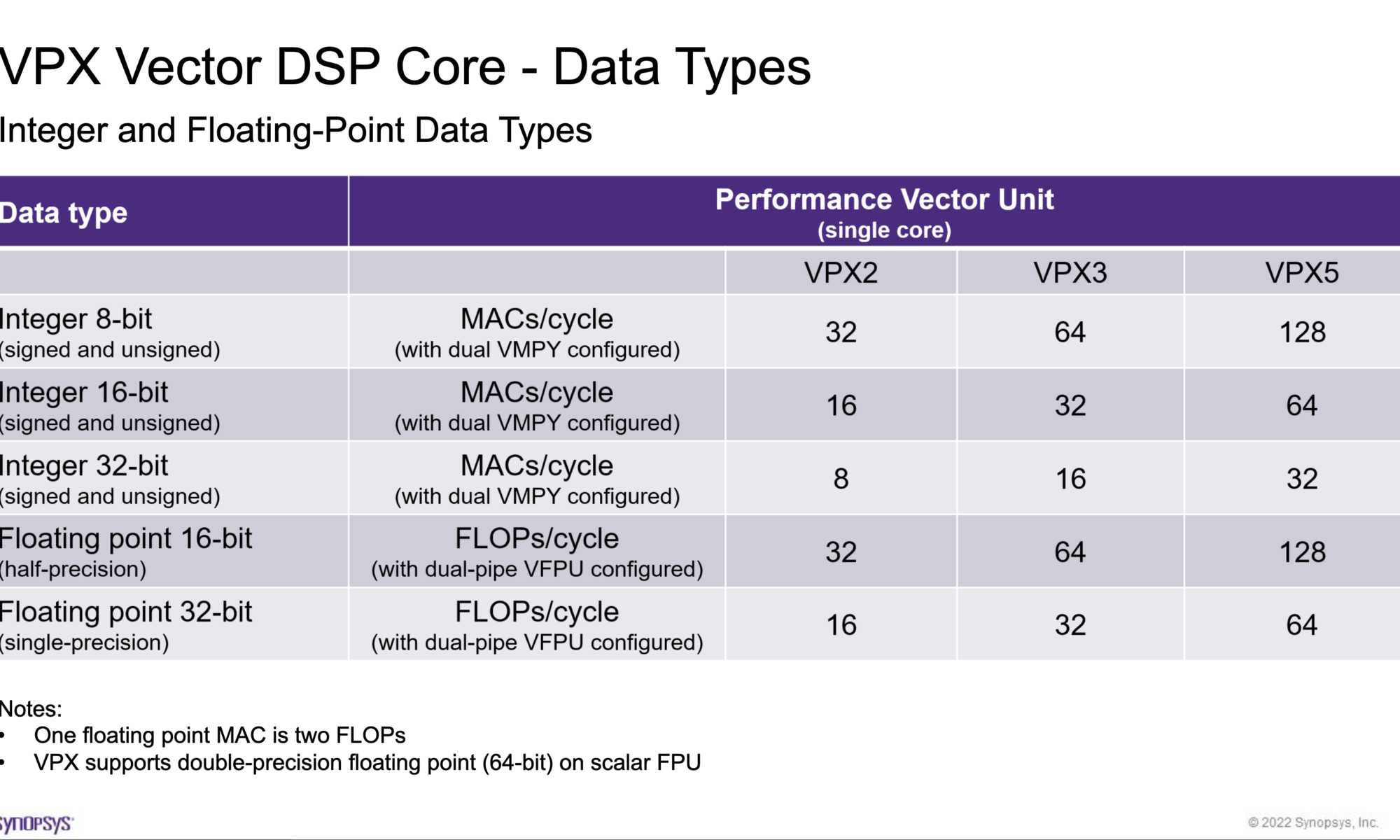

A microphone data stream is of 16-bit integer data type, a camera data can either an 8-bit or 16-bit integer type but a radar data type could be either integer or floating point at 16 or 32 bits. The architecture and the implementation should be versatile enough to handle all these data types and allow the compute resource to be shared among a mix of workloads.

SoC-level Challenge

An SoC must support efficient data movement through fast DMA to peripherals and system memory. The SoC implementation should also be resilient to high memory latencies. It should deliver a high Fmax for required cycle performance at the same time enable easy timing closure. And of course, the low power consumption, low leakage, small form factor and low-cost are requirements that go hand in hand with these applications.

Don’t Forget the Software

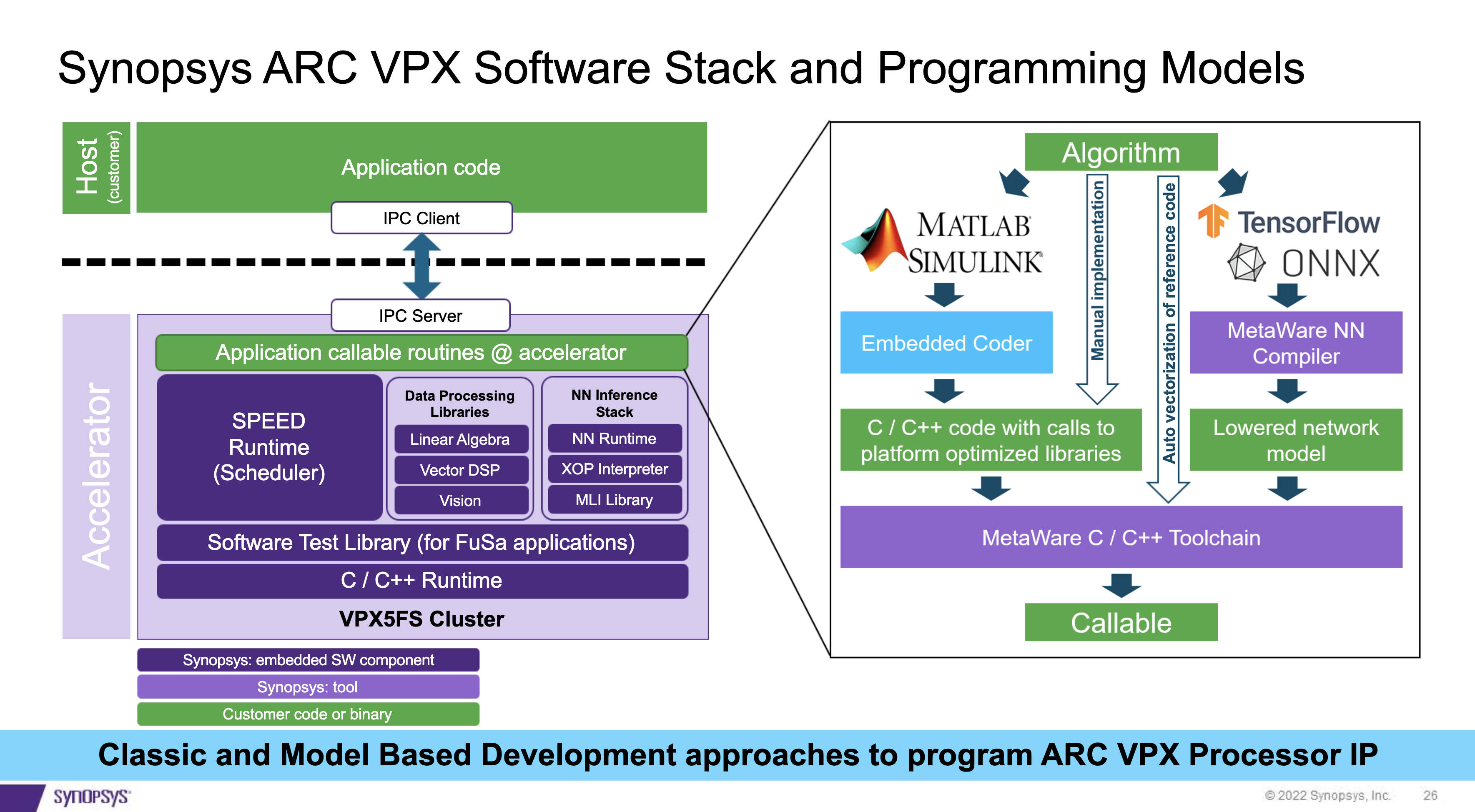

Sensor fusion solutions are not just about hardware optimization. They require development and integration of a variety of software modules for data processing, user interaction, interrupt handlers, drivers, etc., The software code should be easily portable across different DSP IP implementations.

Synopsys’ Offerings for Implementing Sensor Fusion Solutions

Efficient SoC Integration

Synopsys offers an entire family of DSP IP to serve various markets. For sensor fusion applications, the ARC® VPX family of processors is the right match. It is easy to scale an implementation using the pre-integrated multicore DSPs with cache coherency and shared DMA. Whether the SIMD implementation is 128-bit, 256-bit or 512-bit, there is a corresponding processor in the VPX family to support that requirement. There is also the ARC NPX NN accelerator that can be used under the unified programming environment to implement the front-end for ML applications. The VPX processors are highly configurable to achieve performance/area optimizations. These processors also support a variety of data types.

Extensive Set of Software Building Blocks

Synopsys offers a rich set of software building blocks including the Vector DSP library and the Vector Linear Algebra library. These libraries are implemented using Vector-Length Agnostic C/C++ programming model, enabling easy software portability across all members of the VPX family. Also included are the machine language interface library and the NN software development kit.

Summary

In summary, the Synopsys ARC VPX DSP processors offer high performance and scalability, compact form factor, and low power. These processors are compliant with the ISO 26262 ASIL B/D level requirements for automotive safety requirements. Heterogeneous signal-processing workloads can be efficiently and effectively implemented using these processors. It is also easy to integrate with processors from the other members of the Synopsys ARC family of DSP processors.

You can learn more details about the Synopsys ARC VPX DSP Processors here.

Also Read:

Intelligently Optimizing Constrained Random

Using STA with Aging Analysis for Robust IC Designs

Casting Light on OpenLight’s Open Silicon Photonics Platform

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.