I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and came to the US as a teen. He was a very good pianist, good enough to go on music tours and appear on TV shows, an experience he describes as “not necessarily recommended for any kid”. He expected to go to a music conservatory but instead he went to Purdue and studied CEE (what everyone calls CS/EE today). As he likes to say “I studied to be a conductor, and I must have been only semi-good, as I ended up in semi-conductors.”

While supporting VLSIextract and more, Michael went to Santa Clara and got an MBA and also made the transition from engineering into marketing.

In 1999 he joined Numerical Technologies, one of the many DFM startup companies of that era, doing marketing and business development. It was the most successful of those DFM startups, going public in 2000 and being acquired in 2003 by Synopsys for $250M.

Next stop was Cadence where he did various things, including as I mentioned working for me for at time in strategic marketing.

After a couple of years at Cadence, Michael moved to Calypto to be their first VP marketing. They were bringing to market sequential formal verification technology, which was new and innovative technology. Michael drove the first deals and also created a partnership with Mentor which eventually ended up with Mentor taking a majority position in the company and adding their Catapult synthesis to the product portfolio. Of course Calypto still exists today.

Michael joined Synopsys almost six years ago and joined the Verification business group, which has grown steadily to now offering simulation, emulation, static analysis, formal, debug and more.

Michael joined Synopsys almost six years ago and joined the Verification business group, which has grown steadily to now offering simulation, emulation, static analysis, formal, debug and more.

Michael reckons that verification is an area where lots of innovation is happening, at least partially because you can never have enough verification. There has been a big shift in the last few years towards emulation, which has gone from an esoteric segment for the occasional group who can afford a seven-figure sum to part of the mainstream. It has also turned out to be the complementary piece to virtual prototyping.

A lot of the focus of verification these days is to make sure software can be run before tapeout. This is firstly so that the software engineers can start development before silicon is back from the fab. But it is also because if your chip has to run, say, Android, then you really really want to boot Android on a model of the chip before tapeout, no matter how much verification has already been done. Though 90%+ of bugs are still found by simulation, booting Android takes around 40B cycles so you are going to need emulation for it. .

The next step looks like systematic power analysis in the context of verification, in particular emulation with power. So not just “can I boot Android?” but “can I boot Android without frying the chip?”

Another challenge is how best to intelligently combine formal and simulation. If formal verification has proved something, then it is not necessary to prove it again with simulation. On the other hand, simulation results can be intelligently used to lead to good assertions for use in formal.

Synopsys recently expanded its verification investment by acquiring Atrenta, and now they are looking at how to combine static analysis with other techniques to get results faster. One great things about Spyglass (Atrenta’s anchor platform) is that it is used on RTL when the design has only just started to be developed, long before it is in any sense complete. Early feedback on power, DFT and physical issues while the RTL is being created.

Verification does have a big and direct impact on time-to-market, especially due to software bringup. In the days when you had to wait for the chip before software development started, versus today, the schedule can be pulled in by weeks if not months.

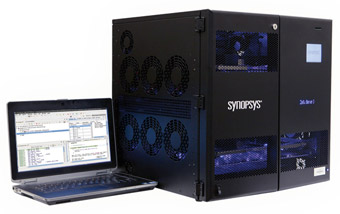

On emulation, as you probably know, Synopsys acquired EVE a couple of years ago. The ZeBu hardware technology was and is based on Xilinx FPGAs so that they can leverage Xilinx’s R&D investment with faster chips every 2-2½ years, and with lower cost than designing their own chips. Many industry leaders are aligning with this strategy as it enables them to keep up with their demands for performance, capacity, and cost. Historically one challenge with emulation (any emulator) is that it took a good amount time and effort (including possible changes to the RTL) to bring a design up in emulation. Synopsys has unified the VCS compile process with ZeBu to significantly shorten this bring up time. Also as another result coming from this project, ZeBu compile time is 3x faster (most designs only take 4 hours and often much less) and if it compile in VCS is should compile on the ZeBu. Synopsys are still #3 in emulation but bridging the gap fast.

On emulation, as you probably know, Synopsys acquired EVE a couple of years ago. The ZeBu hardware technology was and is based on Xilinx FPGAs so that they can leverage Xilinx’s R&D investment with faster chips every 2-2½ years, and with lower cost than designing their own chips. Many industry leaders are aligning with this strategy as it enables them to keep up with their demands for performance, capacity, and cost. Historically one challenge with emulation (any emulator) is that it took a good amount time and effort (including possible changes to the RTL) to bring a design up in emulation. Synopsys has unified the VCS compile process with ZeBu to significantly shorten this bring up time. Also as another result coming from this project, ZeBu compile time is 3x faster (most designs only take 4 hours and often much less) and if it compile in VCS is should compile on the ZeBu. Synopsys are still #3 in emulation but bridging the gap fast.

VIP is another area that is doing well since the interfaces have got so complex that no design group can do verification on their own. For example, the latest USB 3 spec is insanely complex, and there are a dozen interfaces like that. There is an obvious synergy with Synopsys’s IP business since they are #1 in interface IP.

Of course Michael is not going to make some product announcement in the middle of an interview like this, but he did say that, as you would expect, Synopsys is working on all of these areas. “Watch this space” as the saying goes.

Yes, Michael continues to study piano although with his travel schedule he can’t exactly go on concert tours., He studied for many year (started when he was at VLSI) with a former professor of the Vienna Conservatory. More recently, he’s been taking lessons at Stanford. It turns out that there are a surprising number of people at Stanford studying both music and engineering. Apparently math, music, language and computer science all use the same part of the brain so often people who are good at one on the list are good at another.

See also John Koeter: How To Be #1 in Interface IP

See also Synopsys’ Andreas Kuehlmann on Software Development

See also Antun Domic, on Synopsys’ Secret Sauce in Design

See also Bijan Kiani Talks Synopsys Custom Layout and More

Comments

0 Replies to “Michael Sanie Plays the Synopsys Verification Variations”

You must register or log in to view/post comments.