Compute Express Link (CXL), a new open interconnect standard, targets intensive workloads for CPUs and purpose-built accelerators where efficient, coherent memory access between a host and device is required. A consortium to enable this new standard is in place, and a lot of heavy hitters are behind the standard, including IP support from Synopsys. If you want to learn more about CXL, Synopsys offers a good overview here. As the number two IP provider in the industry, Synopsys backing CXL is a big deal. I probed a bit to find out how Synopsys is extending CXL applications with new IP.

CXL is not new to Synopsys. As reported on SemiWiki in 2019, Synopsys was the first IP provider with a complete CXL implementation. Arm also puts its weight behind CXL back in 2019. This turns out to be important for a number of reasons, as you will see in a moment. I recently had the chance to catch up with Gary Ruggles, senior product marketing manager at Synopsys. I wanted to understand a bit more about CXL technology, the consortium and how Synopsys is extending CXL applications with new IP. Gary is a veteran of chip design and IP. He’s worked at several IP companies including Arm before joining Synopsys. He’s also assisted customers with IP requirements for ASIC, including a stint at eSilicon, my alma mater.

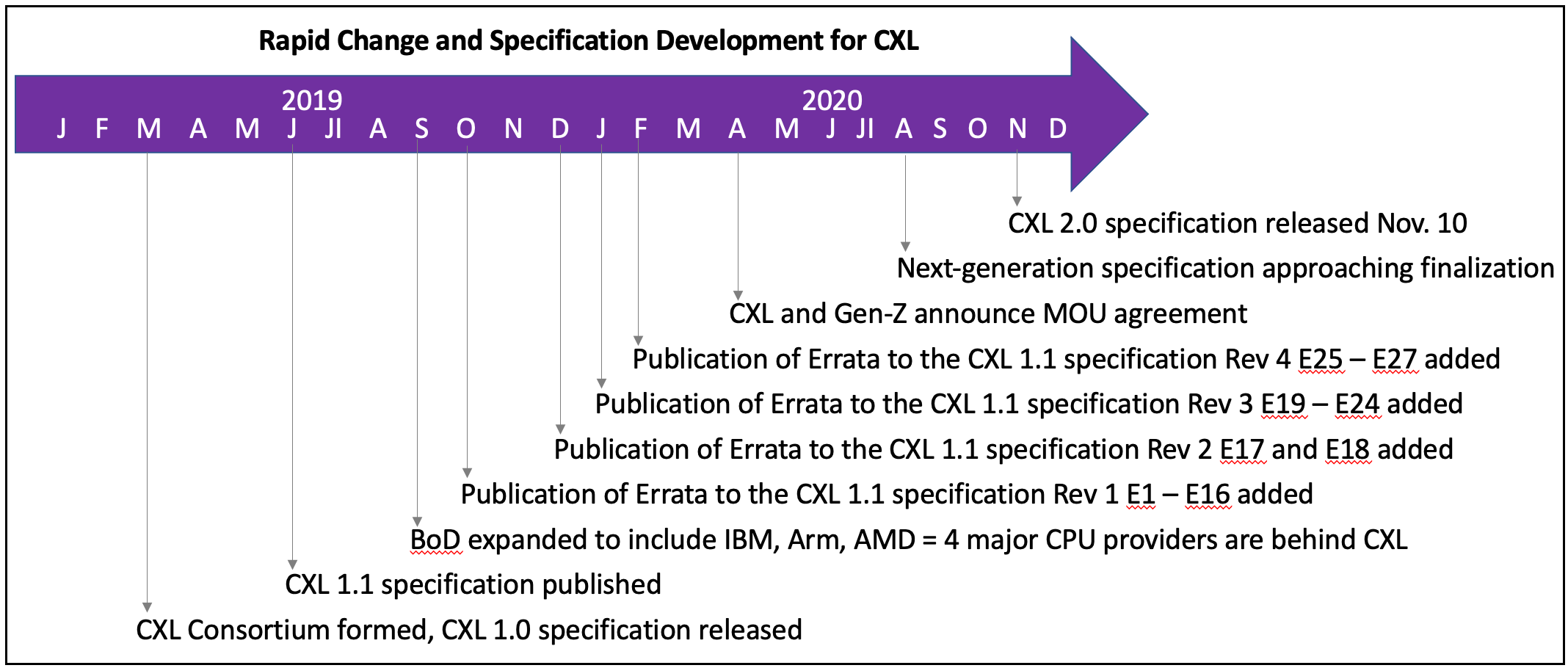

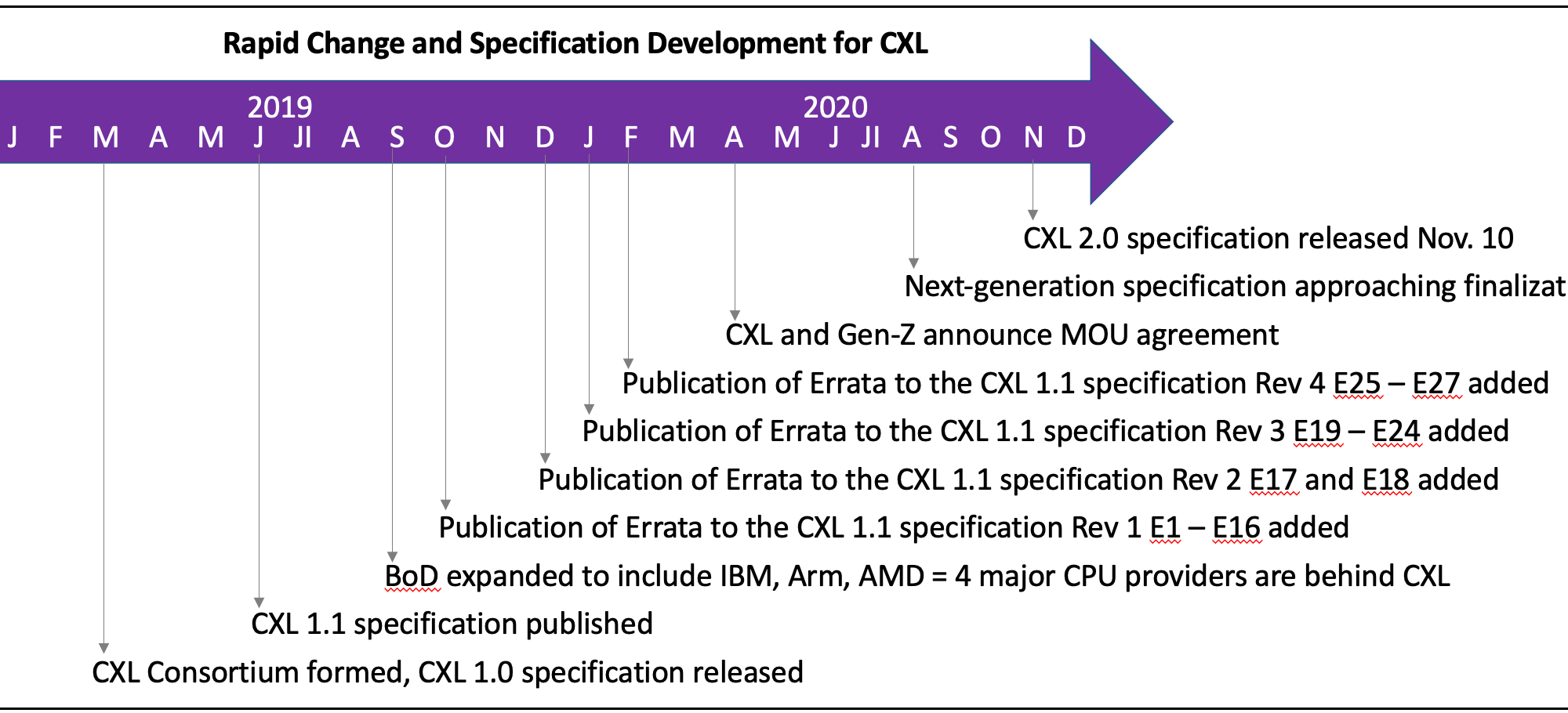

The first thing Gary explained was that the CXL consortium has been very busy. The headline graphic above illustrates the rapid expansion of the specification. There are over 120 members in the consortium. It is clearly the largest of the new high-speed interconnect/coherency standard consortiums, eclipsing membership in Cache Coherent Interconnect for Accelerators (CCIX) consortium with about 50 members, Gen-Z with approximately 70 members, and OpenCAPI with around 38 members. The CXL Consortium was formed about 18 months ago compared to nearly four years ago for the other two, so CXL has definitely hit a nerve with a lot of influential companies. I previously mentioned heavy hitters. Consider that the CXL Board of Directors includes Intel, IBM, AMD and Arm. So, the four major CPU makers are all behind CXL. This is change-the-world kind of stuff in my opinion.

Gary also pointed out that there is a memorandum of understanding (MOU) between the CXL and Gen-Z Consortiums. With this Gen-Z MOU in place, CXL is becoming the dominant solution inside servers. Gen-Z can now offer connectivity from box-to-box or even rack-to-rack, leveraging its ability to use Ethernet physical layers to get longer reach connectivity than CXL can achieve using PCIe 5.0 PHYs. The footprint for CXL is growing.

We also discussed future enhancements. Since the CXL 2.0 specification was just released on November 10th, it is now clear that it’s all about enabling storage applications. The bulk of the new features added to the CXL 2.0 specification are focused in this area and include:

- Switching for CXL.mem

- Pooled memory that can be shared by more than one DS port

- Managed hot-plug support (enabling storage device removal)

- Security/encryption support

With switching added, memory that is attached to multiple downstream devices may be able to be shared across multiple hosts, and the memory can be split among those hosts as needed for a particular application. This opens up many new architectural considerations.

There is a lot more to the CXL story, including potential for CCIX over CXL, which further extends the possibilities. Gary has written a very informative technical bulletin on the topic and you can access a copy of it here. There is one more interesting development I’ll mention. Synopsys recently announced its DesignWare® CXL IP supports AMBA CXS protocol to enable seamless integration with scalable Arm® Neoverse™ Coherent Mesh Networks. This capability delivers an optimized multichip IP stack for a range of high-performance computing, datacenter, and networking applications. You can read the full press release here.

You can learn more about Synopsys IP support for CXL, both current and future, here. You will clearly see how Synopsys is extending CXL applications with new IP.

Also Read:

Synopsys talks about their DesignWare USB4 PHY at TSMC’s OIP

AI/ML SoCs Get a Boost from Synopsys IP on TSMC’s 7nm and 5nm

Share this post via:

Comments

2 Replies to “Synopsys is Extending CXL Applications with New IP”

You must register or log in to view/post comments.