On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single SoC?

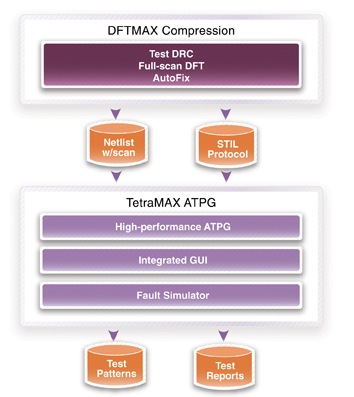

A recent White Paperfrom the engineers at ARMand Synopsysshowed exactly how to do this trade-off using an EDA tool called TetraMAX ATPG along with test-compression hardware called DFTMAX.

Non-shared IO Approach

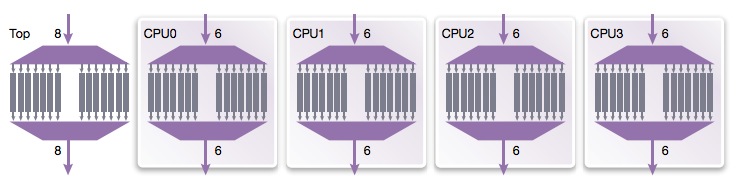

Let’s say that you have designed with a quad-core ARM Cortex-A15 or A7 processors, and are using:

- Hardware compression

- 6 scan channels per CPU core (x4 cores)

- 8 scan channel for non-CPU logic

- Total of 32 I/O pairs for testing

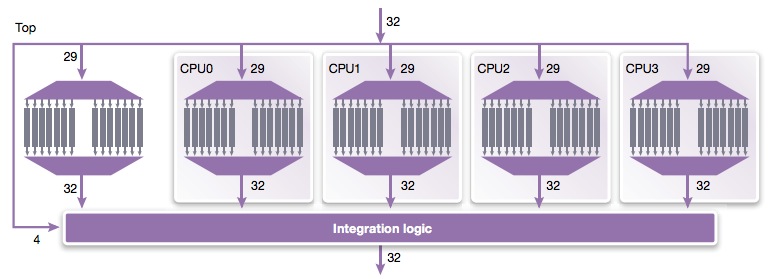

Non-CPU test logic on the left, four cores on the right

Each core has separate test channels for inputs and outputs, so nothing is being shared between cores for testing.

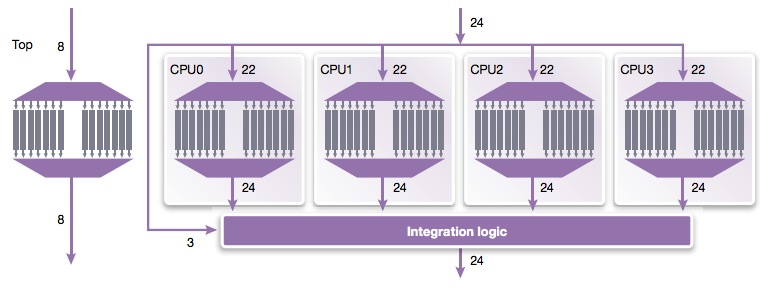

Mixed-share IO Approach

A different test approach from non-shared is to share IO pins and increase the width of test IOs per CPU from 6 to 22.

Mixed-shared IO

With this mixed-shared IO approach with 22 scan inputs per CPU core we can reduce the number of test patterns required compared to the 6 scan input non-shared approach.

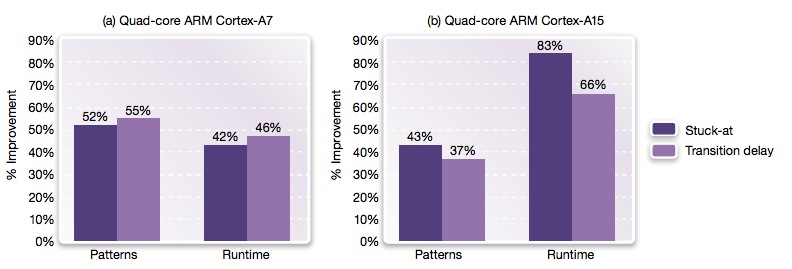

Improvements in Patterns and Runtime compared with Non-shared

Both stuck-at and transition delay fault tests show improvements with this shared IO approach. The test results for the quad-core Cortex-A15 are quite dramatic at 83% improvement in runtime.

All-shared IO Approach

A third approach is to share scan inputs for non-CPU and CPU channels.

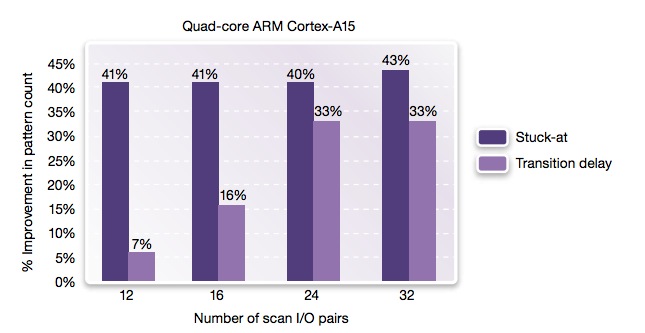

The following chart shows the improvement in pattern count as a function of the number of scan IO pairs: 12, 16, 24 and 32 scan IO pairs

Improvements in pattern counts vs. number of Scan IO pairs

The stuck-at fault improvements are almost constant at 40% to 43% improvement over the range of IO pairs, however the transition delay improvements vary greatly from 7% at just 12 IO pairs up to 33% at 32 IO pairs.

At the 24 and 32 scan IOs the improvements with all-shared are quite similar to the mixed-shared IO results. The all-shared IO approach is attractive to reduce test costs when pin resources are limited.

Summary

IP re-use is widely used today to enable quicker time to market for SoCs. Using multiple ARM cores and other multicore processors can be a test challenge. Three test approaches were presented that compared results using hardware compression to reduce pattern count reductions as a function of the number of scan IO pairs.

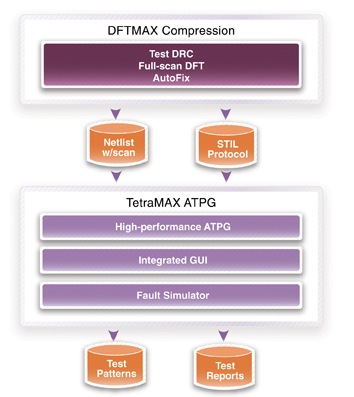

Synopsys offers test compression in DFTMAX, along with test pattern generation software in TetraMAX ATPG that allows design and test engineers to make these test trade-off decisions.

Read the complete White Paper here.

lang: en_US

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.