Deep learning, modeled (loosely) on the way living neurons interact, has achieved amazing success in automating recognition tasks, from recognizing images more accurately in some cases than we or even experts can, to recognizing speech and written text. The engineering behind this technology revolution continues to advance… Read More

Tag: compression

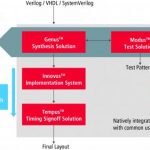

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

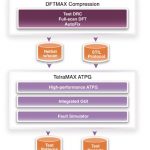

What’s next in test compression?

If you’ll be at ITC TestWeek in Seattle (Oct 20-23), here’s one event you don’t want to miss: a technology reception hosted by Mentor, with Janusz Rajski and Nilanjan Mukherjee as the featured speakers. It is free to ITC attendees and you can register here. [If for some crazy reason you haven’t registered for ITC yet, do that… Read More

Minimize the Cost of Testing ARM® Processor-based Designs and Other Multicore SoCs

On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single… Read More