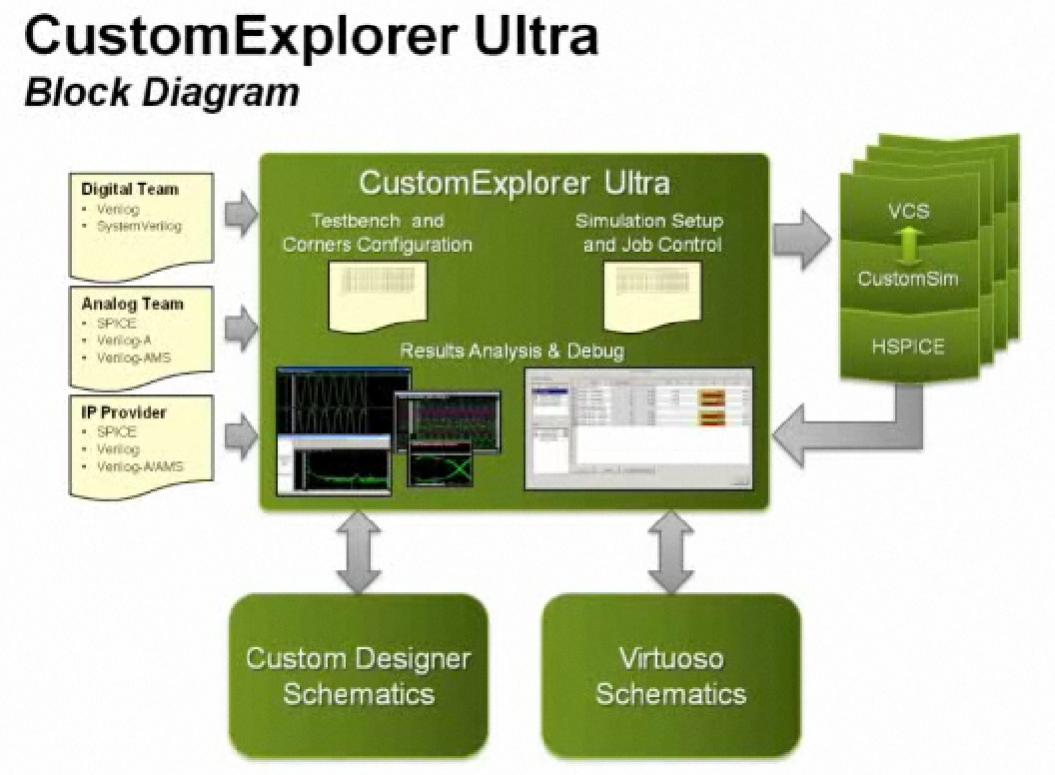

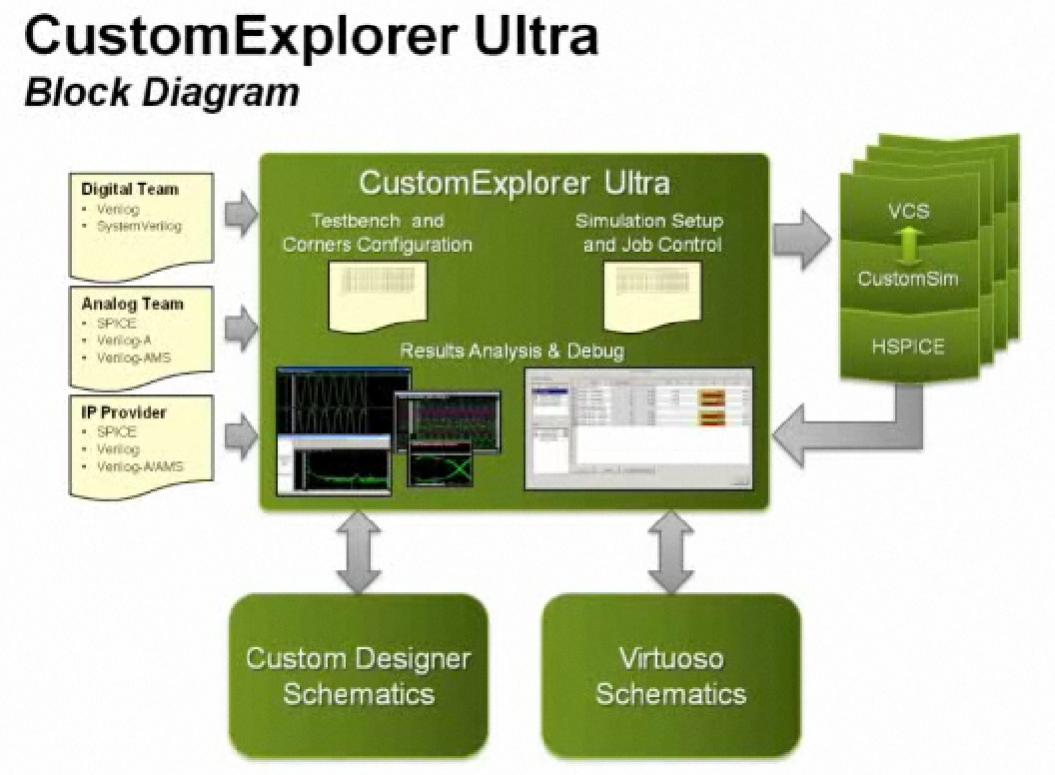

I attended the Synopsys webinar today for a tool called Custom Explorer Ultra (CXU). Product details on the Synopsys web site are here. The CXU tool would be used by AMS designers that want to setup, control and view results from simulators like HSPICE, CustomSim or VCS on transistor-level and AMS designs.

The webinar was scheduled for 10:00AM so I logged in early at 9:54AM and waited for the event to start, to my surprise the webinar abruptly started on slide #2 mid-sentence, so I missed the introduction and slide #1 somehow.

Because Cadence has a dominant position in transistor-level design Synopsys has added support for Cadence Virtuoso schematics in their CXU tool. During the Q&A period Duncan McDonald mentioned that CXU also works with the Cadence Spectre and Mentor Eldo circuit simulators, although the demo that I saw today didn’t show those options in the GUI, probably an add-on option. I also heard that FineSim is supported with CXU and asked that question during the webinar, although I didn’t see FineSim in the GUI options.

During the Q&A time only three questions were answered and then the webinar was over in spite of me typing in questions and not getting answers. Clearly there is room for improvement and it was odd because I’ve attended other Synopsys webinars where many questions were taken and answered.

Demo 1

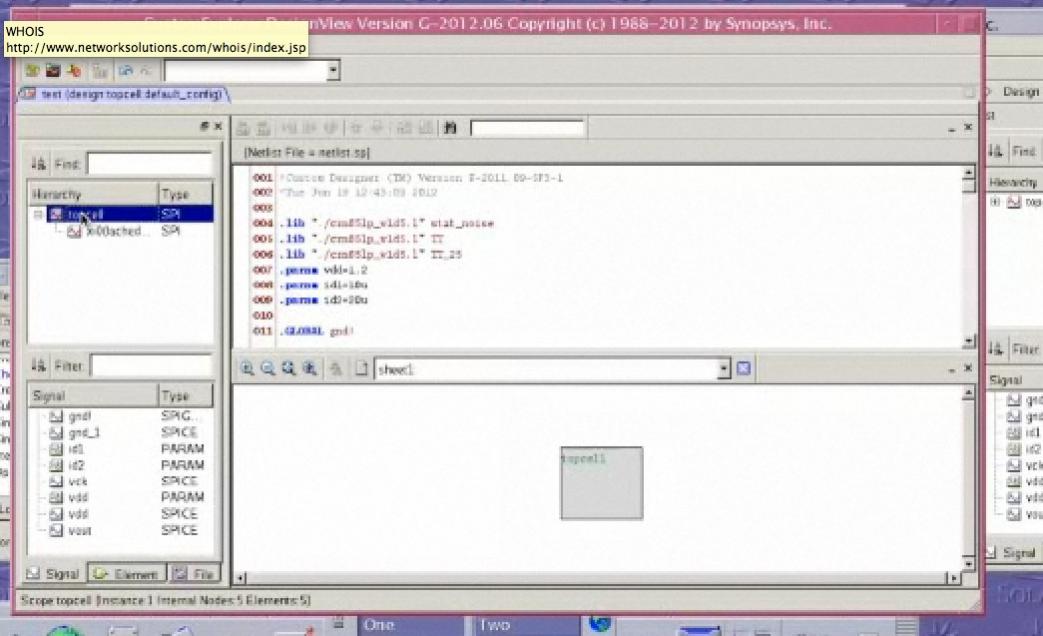

Read a SPICE netlist and simulate it with HSPICE.

Explore the netlist using a GUI. Traverse the netlist hierarchy graphically.

Find all MOS devices by W/L values.

Find the PWL sources in a netlist and then save them for re-use in another design.

Debug your netlist by checking syntax, connectivity, ERC (Electrical Rule Checks).

Cross probe between the created schematic and the netlist.

Demo 2

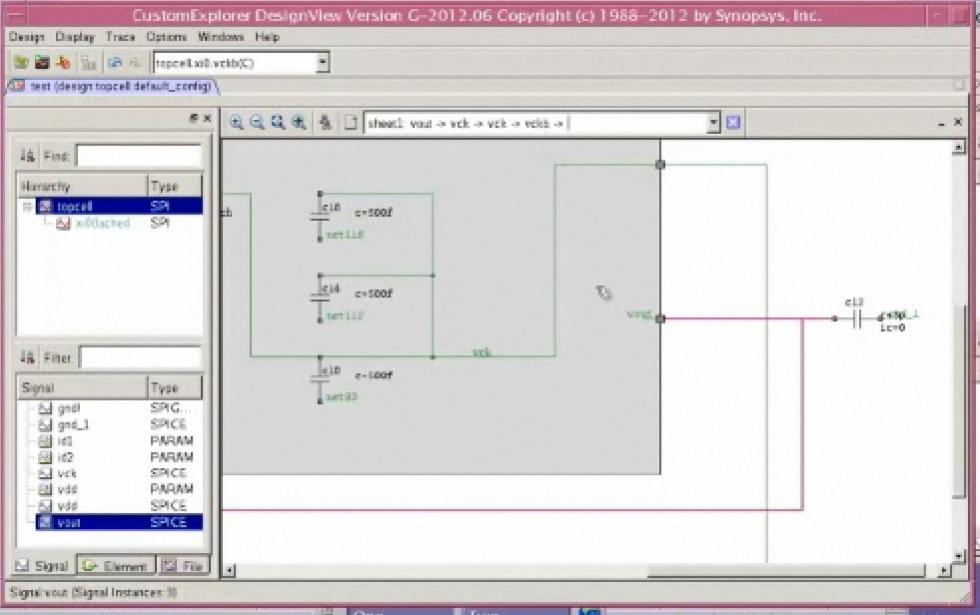

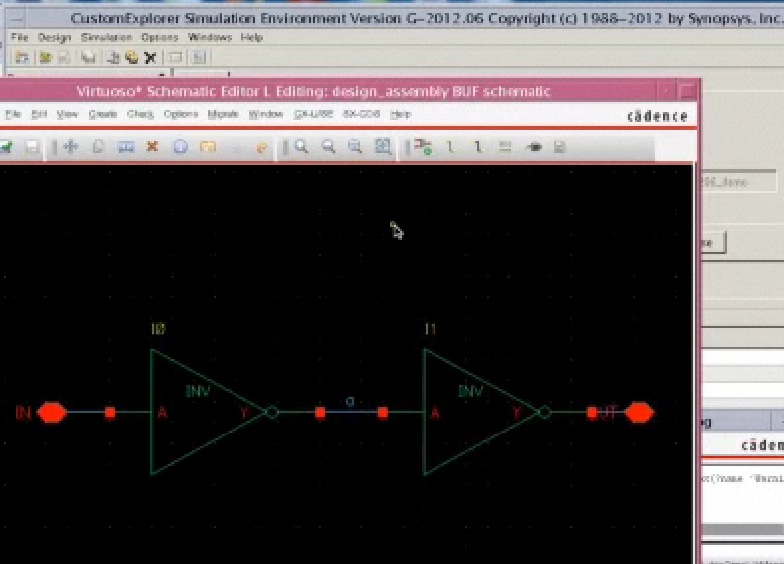

Customer Designer (Schematics) + Custom Explorer demo: Charge Pump design

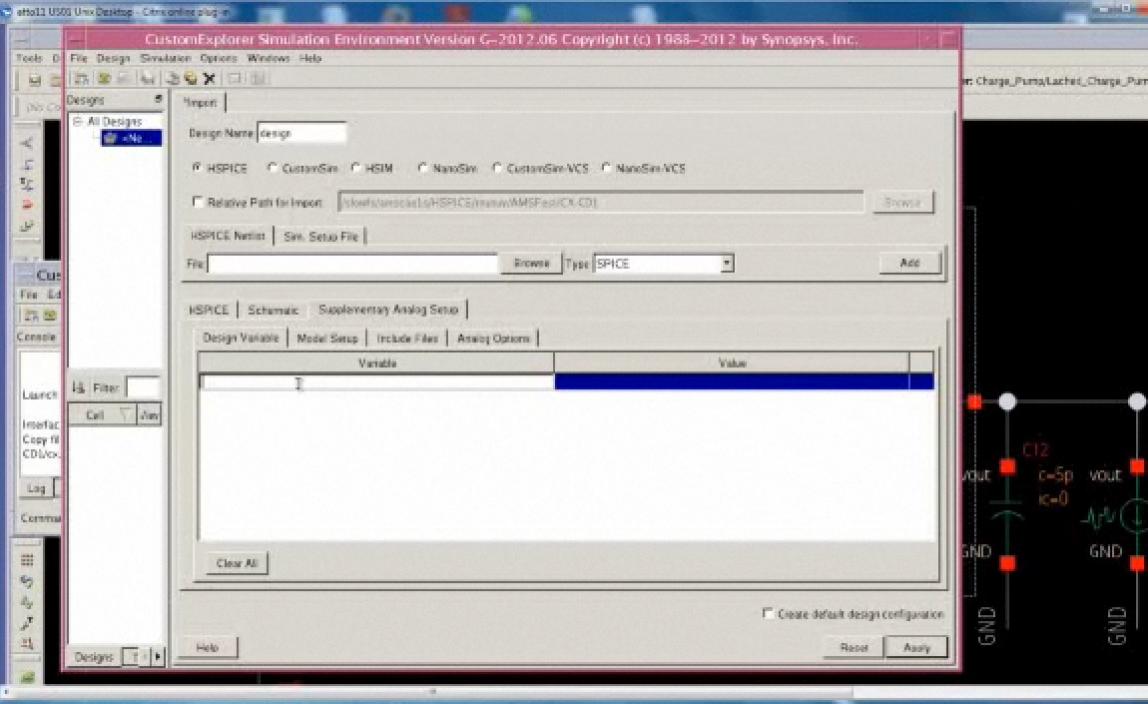

Open up a schematic, invoke CXU, add the netlist to CXU, add model files with corners, add design variables, create a configuration for the design.

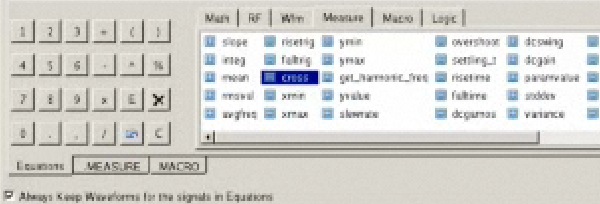

Create a testbench for the configuration: Sweep ID1 across three values. Select HSPICE as the circuit simulator and select Sweep. Select a list of signals to probe on the schematic. Add some HSPICE measurements (Max voltage value between two time points). Add a second HSPICE measurement.

A second testbench is created called ID2 as a Sweep with three values.

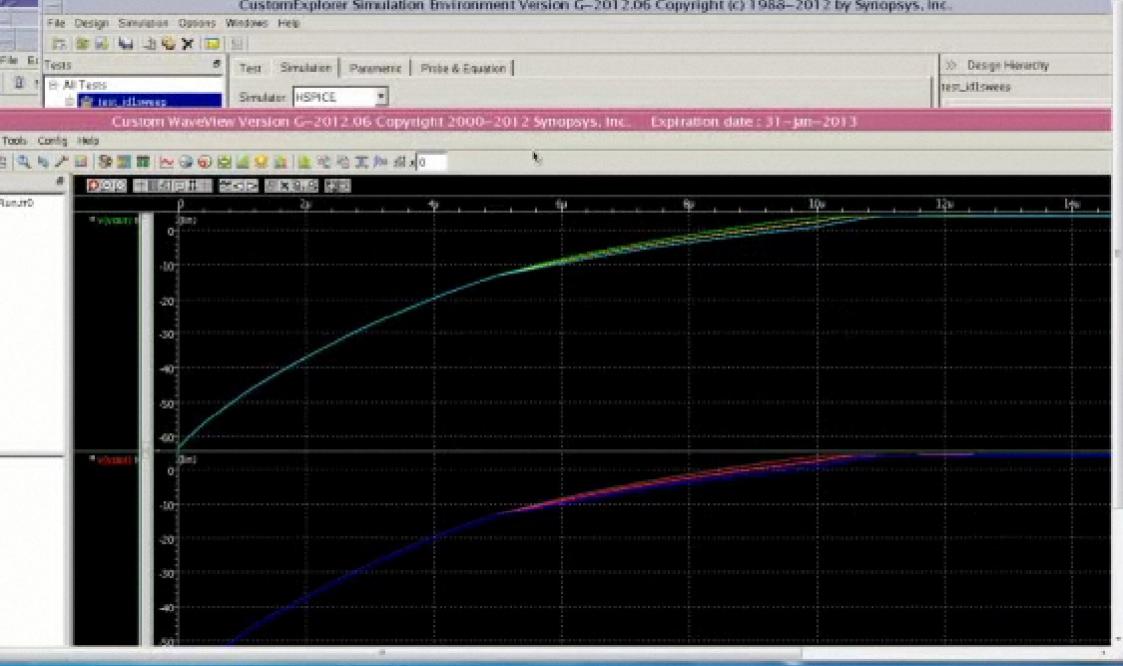

Run HSPICE with both testbenches just defined. View the probe signals, which is Vout.

Result Analyzer has a table of results from the signals we probed.

Cross-probing between schematic and waveform viewer. Trace signals by clicking a schematic pin instance, see highlighted schematic.

Demo 3

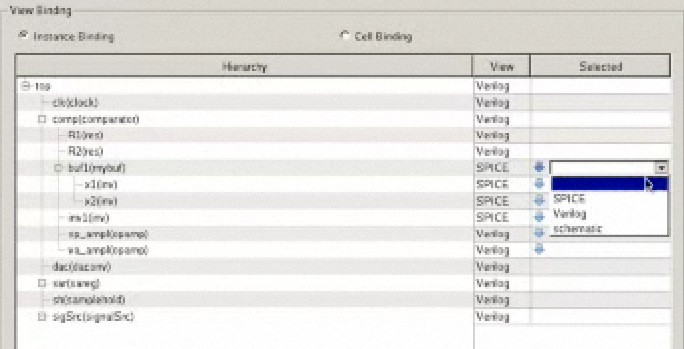

With Virtuoso and CXU, comparator block with Verilog and SPICE models.

Choose CustomSim-VCS as the HDL simulator. Co-simulation run file is required. Schematic for Virtuoso is invoked with an added menu for CXU from Synopsys. Configure the design to use both Verilog an Schematics. Create a testbench and choose VCS commands. Multiple corners can be selected in the GUI. Temperature with three values selected.

Add a list of schematic signals to probe graphically, add them to plot list. Calculations can be made using probed signals, lots of functions to be selected.

A second testbench was added by re-loading the first testbench. Changed a CustomSim value in this testbench.

Selected all corners from each testbench, run simulation, view probes.

Use the Results Analyzer to see values in a table-like format. Cross probing between Virtuoso schematics and CXU viewer. Traced an object from CXU to highlight in schematic any signal.

Q&A

Q: Which Simulators?

A: All analog/digital simulators from Synopsys plus: Spectre, Eldo.

Q: Can you cross-probe an existing waveform analysis?

A: Yes, you can.

Summary

CXU is a capable environment for AMS designers that want to setup, control and view simulation results from HSPICE, VCS and CustomSim. Even users with Virtuoso schematics, Spectre simulator or Eldo simulator can find some value in using CXU. View the webinar.

Synopsys is playing catch-up in this EDA tool area compared to Cadence, Mentor and Tanner EDA since schematic capture is only a few years old at Synopsys.

I still want to know the detailed product roadmap at Synopsys for circuit simulators after the Magma acquisition:

- HSPICE

- FineSim SPICE

- HSIM

- CustomSim

- FineSim PRO

- XA

Comments

There are no comments yet.

You must register or log in to view/post comments.